RESEARCH ARTICLE | JUNE 12 2025

# Quantitative characterization of ZrO₂ gate dielectric interface with tellurium *⊙*

Kyeong-Jae Byeon 💿 ; I. K. M. Reaz Rahman 💿 ; Inha Kim 💿 ; Howoo Park 💿 ; Ali Javey 🗷 💿

Appl. Phys. Lett. 126, 232110 (2025) https://doi.org/10.1063/5.0267586

A CHORUS

# Articles You May Be Interested In

Influence of post-deposition annealing on interfacial properties between GaN and  $\rm ZrO_2$  grown by atomic layer deposition

Appl. Phys. Lett. (October 2014)

Atomic layer deposition of  $ZrO_2$  as gate dielectrics for AlGaN/GaN metal-insulator-semiconductor high electron mobility transistors on silicon

Appl. Phys. Lett. (October 2013)

High quality interfaces of InAs-on-insulator field-effect transistors with ZrO<sub>2</sub> gate dielectrics

Appl. Phys. Lett. (April 2013)

# Quantitative characterization of ZrO<sub>2</sub> gate dielectric interface with tellurium

Cite as: Appl. Phys. Lett. 126, 232110 (2025); doi: 10.1063/5.0267586 Submitted: 25 February 2025 · Accepted: 28 May 2025 · Published Online: 12 June 2025

Kyeong-Jae Byeon, 1,2,3 🕞 I. K. M. Reaz Rahman, 1,2 🕞 Inha Kim, 1,2 🕞 Howoo Park, 3 🕞 and Ali Javey 1,2,4,a) 🕞

# **AFFILIATIONS**

- $^1$ Electrical Engineering and Computer Sciences, University of California, Berkeley, Berkeley, California 94720, USA

- <sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA

- System LSI Division, Samsung Electronics, Hwaseong-si, Gyeonggi-do 18448, Republic of Korea

- <sup>4</sup>Kavli Energy NanoScience Institute, University of California, Berkeley, Berkeley, California 94720, USA

## **ABSTRACT**

Tellurium (Te) has recently emerged as a promising p-type semiconductor that can be processed at low temperatures, compatible with back end of line CMOS integration. Characterization of tellurium-dielectric interfaces is essential for further device advancements. Here, the interface quality of Te with ZrO2 gate dielectric is studied in a metal-oxide semiconductor capacitor structure. The interface trap density (Dit) is measured as a function of atomic layer deposition (ALD) temperature, without the use of a seed layer. Given the low thermal budget of Te, the ALD temperature is shown to be particularly important. The lowest  $D_{it}$  of  $5 \times 10^{12}$  states/cm<sup>2</sup> eV is obtained at a low ALD process temperature of 120 °C. To further assess the impact of Dit on device performance, field-effect transistors (FETs) were fabricated. The subthreshold swing and effective hole mobility of the FETs were analyzed in relation to Dit emphasizing the importance of a defect-minimized interface for enhancing Te transistor performance.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0267586

Tellurium (Te) is a p-type semiconductor that has emerged as a promising candidate for next-generation semiconductor devices due to its unique properties, including high hole mobility and a thicknessdependent bandgap, which ranges from 0.31 eV in bulk to 1.04 eV in the monolayer. 1-3 Notably, evaporated Te can be deposited over large areas at low temperatures, making it an attractive material for optoelectronics and flexible electronics as well as circuit integration. 4-8 Despite recent advancements, research on the Te/gate dielectric interface remains limited. Moreover, the high vapor pressure of Te above 250 °C constrains studies on its interface with gate dielectrics that require high processing temperatures, such as thermally oxidized  $SiO_2$ .

As transistor channel lengths are scaled down, the oxide thickness must also be reduced to meet voltage requirements. However, this results in high levels of leakage currents in ultra-thin oxide layers. One approach to mitigate this issue is to use high- $\kappa$  dielectrics, which maintain the same gate electrostatics with a thicker dielectric film. 11- $ZrO_2$  is a widely studied high- $\kappa$  dielectric with low leakage current and suitability for deposition at low temperatures. 11,14,15 In this study, we focus on characterizing the interface between evaporated Te and atomic layer deposition (ALD)-grown ZrO2 as a function of ALD temperature, without the use of a seed layer. Te-based capacitors with ZrO<sub>2</sub> gate dielectric were fabricated. Capacitance-voltage (C-V<sub>G</sub>) and conductance-frequency (G/ω-f) measurements were performed to extract the interface trap density (Dit). Dit is found to increase at higher ALD temperature, with the lowest extracted value of  $5 \times 10^{12}$ states/cm<sup>2</sup>·eV observed at 120 °C. Additionally, Te-ZrO<sub>2</sub> based fieldeffect transistors (FETs) were fabricated at various ALD temperatures and characterized using current-voltage (I-V<sub>G</sub>) measurements to assess device properties corresponding to each Dit level.

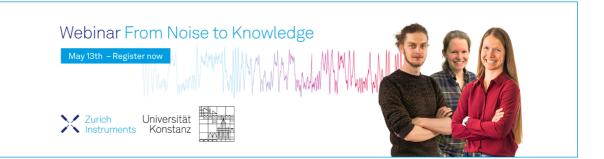

A quartz substrate was used for fabrication of metal-oxidesemiconductor (MOS) capacitors to minimize parasitic capacitance. Figure 1(a) shows the schematic of a Te MOS capacitor with a bottom electrode contact and a top-gate with ZrO2 as the gate dielectric. The fabrication process involves defining the bottom electrode area using standard photolithography at the first step, followed by deposition of 30 nm thick rhodium (Rh) via e-beam evaporation as the metal contact. The Te region was then patterned using photolithography to cover both the bottom electrode and the quartz surface. An 8 nm thick amorphous Te layer was thermally evaporated at −80 °C to achieve a uniform film. 16 Te undergoes an amorphous to crystalline phase transition near ambient conditions due to the low activation energy. A low

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed: ajavey@berkeley.edu

FIG. 1. (a) Cross-sectional schematic of the device structure and measurement setup used for C–V and G/ $\omega$ -frequency measurements. (b) and (c) Optical microscope images of SB and MB capacitors, respectively. (d) XPS measurement results of an 8 nm Te layer on a Si substrate. (e) C–V characteristics at room temperature for an SB Te capacitor with an ALD temperature of 120 °C. The AC amplitude is 25 mV.

substrate temperature during crystallization limits the nucleation site formation and reduces grain boundaries. The substrate temperature was maintained below 5 °C during crystallization, to achieve crystalline Te with grain sizes exceeding several micrometers. Afterward, the Te was lifted off, and a 10 nm thick ZrO2 layer was deposited across the entire surface using ALD at temperatures of 120, 150, and 180 °C. Te spontaneously oxidizes upon exposure to air, forming a native oxide layer with a thickness of up to approximately 0.4 nm. <sup>17</sup> For the remainder of this study, we refer to the resulting Te-TeO<sub>2</sub>-ZrO<sub>2</sub> interface as the Te-ZrO2 stack. Next, the gate electrode was patterned on the Te-ZrO<sub>2</sub> stack, followed by the deposition of a 2 nm Ti/30 nm Au gate electrode via e-beam evaporation and subsequent liftoff. To ensure reliable probing, the ZrO2 layer over the contact pad region was etched using a buffered oxide etchant. Finally, single-bridge (SB) and multibridge (MB) capacitors were fabricated to examine the impact of grain boundaries on interface trap density, with the MB structure divided into nine separate identical regions, as shown in Figs. 1(b) and 1(c). The total active areas of the SB and MB capacitors were 383 and  $435 \,\mu\text{m}^2$ , respectively. The MB design minimized the influence of grain boundaries at the Te-ZrO<sub>2</sub> interface by segmenting the active area into smaller regions, with each bridge area smaller than an individual grain. C-V measurements were then performed, as shown in Fig. 1(a).

To promote ALD of  $ZrO_2$  on the Te surface, a thin Te oxide layer is necessary to provide  $TeO_2$ –OH\* sites for the adsorption of Zr ALD precursors. <sup>14,18</sup> X-ray photoelectron spectroscopy (XPS) measurements on a representative 8 nm thick Te film confirmed the presence of  $TeO_2$ , as shown in Fig. 1(d). Figure 1(e) presents the frequency-dependent  $C-V_G$  characteristics at ambient temperature for the SB capacitor with a  $ZrO_2$  gate dielectric deposited at an ALD temperature of  $120\,^{\circ}$ C.  $TeO_2$  is a p-type semiconductor with high hole mobility. <sup>19,20</sup> Therefore, any interface trap is likely to form at the interface between  $Te-TeO_2$  and  $ZrO_2$ . To account for the influence of the thin interfacial

oxide, the gate capacitance was extracted from the C–V $_{\rm G}$  characteristics at V $_{\rm G}=-1.0$  V, yielding a value of 0.67  $\mu$ F/cm $^2$ . In the full depletion region (V $_{\rm G}>1.5$  V), frequency-dependent capacitance dispersion was observed, which is attributed to the reduced response of minority carriers (electrons) at high frequencies, consistent with the typical behavior of conventional p-type metal-oxide-semiconductor (MOS) capacitors in CMOS technology. However, at frequencies above 500 kHz, a substantial decrease in capacitance was observed across the entire C–V curve. This behavior is attributed to the presence of deep trap states at the Te–ZrO $_2$  interface, which hinder the ability of charges to respond to high-frequency signals. $^{21-25}$  As shown in Fig. S1, the C–V curves of all capacitors with ZrO $_2$  ALD temperatures of 120, 150, and 180 °C exhibited similar trends in frequency dispersion and a significant reduction in capacitance at high frequencies.

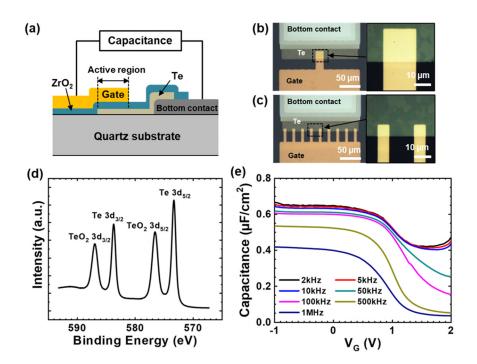

The conductance method was used to extract  $G/\omega$ -f and calculate  $D_{ib}^{26-28}$  as shown in Figs. 2(a)–2(c). The measured conductance  $(G_m)$  was derived from the measured dissipation factor  $(D_m)$  and measured capacitance  $(C_m)$  as  $G_m = D_m \omega C_m$ . The corrected capacitance  $(C_c)$  and corrected conductance  $(G_c)$  were obtained from the measured capacitance  $(C_{ma})$  and conductance  $(G_{ma})$  in the accumulation region. These values were then used to determine the sheet resistance  $(R_s)$  as follows:

$$R_{s} = G_{ma} / (G_{ma}^{2} + \omega^{2} C_{ma}^{2}). \tag{1}$$

Based on  $R_s$ , the series resistance factor (a) was calculated as  $\alpha\!=\!G_m-({G_m}^2+\omega^2{C_m}^2)\,R_s.$  Subsequently, the corrected capacitance and corrected conductance were determined using the following equations:

$$G_c = \left[ \left( G_m^2 + \omega^2 C_m^2 \right) \mathbf{a} \right] / \left( \mathbf{a}^2 + \omega^2 C_m^2 \right), \tag{2}$$

$$C_c = \left[ \left( G_m^2 + \omega^2 C_m^2 \right) C_m \right] / \left( \alpha^2 + \omega^2 C_m^2 \right). \tag{3}$$

**FIG. 2.** (a) Equivalent circuit of a Te capacitor. (b) Simplified circuit layout of (a). (c) Equivalent circuit measured using the experimental setup, where  $C_{it}$  and  $R_{it}$  represent the interface trap capacitance and resistance, respectively, and  $C_p$  denotes the equivalent parallel substrate capacitance. (d)  $G/\omega$  vs frequency for the SB capacitor with an ALD temperature of 120 °C. (e)  $D_{it}$  vs  $E-E_{V_i}$  calculated from the peak of  $G/\omega$  vs frequency.

Finally, the equivalent parallel conductance  $(G_p/\omega)$  and  $D_{it}$  were expressed as

$$G_p/\omega = \omega G_c C_G^2 / [G_c^2 + \omega^2 (C_G - C_c)^2],$$

(4)

$$D_{it} = (2.5/q) \left( G_p / \omega \right), \tag{5}$$

where G<sub>p</sub> represents the equivalent parallel conductance. Based on these equations, the  $G_p/\omega$ -f of the SB capacitor with a ZrO<sub>2</sub> dielectric deposited at an ALD temperature of 120 °C was plotted as a function of  $V_G$ , ranging from 1.9 to 1.3 V, as shown in Fig. 2(d). The  $G_p/\omega$ -f plots in the full depletion region for all capacitors at various ZrO2 ALD temperatures are presented in Fig. S2. Subsequently, Dit was extracted using the maximum peak values in the  $G_p/\omega$ -f curves. Figure 2(e) presents the D<sub>it</sub> values for SB and MB capacitors with ZrO<sub>2</sub> gate dielectric deposited at ALD temperatures of 120, 150, and 180 °C. Considering that 8 nm-thick Te has a bandgap of approximately 0.5 eV,6 the lowest Dit value observed in our measurements was  $5 \times 10^{12} \text{ states/cm}^2 \cdot \text{eV}$  at the midgap for the MB capacitor with  $\text{ZrO}_2$ deposited at 120 °C, while Dit increased at higher ALD temperatures. Under identical ALD conditions, SB capacitors consistently exhibited a higher Dit than MB capacitors. Notably, Dit of the MB capacitor with ZrO<sub>2</sub> deposited at 150 °C was reduced by approximately 71% compared to that of the SB capacitor at the same ALD temperature. This Dit reduction in MB capacitors is attributed to the mitigation of Te grain boundary effects at the Te-ZrO2 interface, achieved by segmenting the active capacitor area. However, both SB and MB capacitors fabricated at an ALD temperature of 180°C exhibited a significant degradation in interface quality, with Dit exceeding  $3.6 \times 10^{13}$  states/cm<sup>2</sup>·eV.

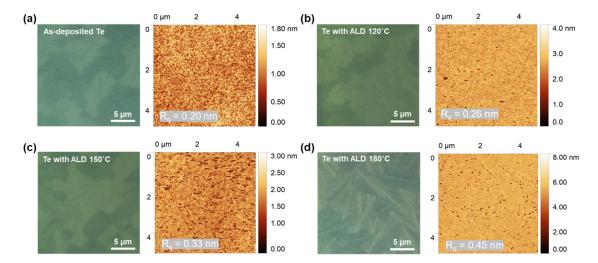

To investigate the variation in  $D_{it}$  with  $ZrO_2$  ALD temperature, the Te regions of the capacitors were examined using optical microscopy. The Te grain size showed no significant difference compared to the as-deposited films after the  $ZrO_2$  deposition at a process temperature of 120 and 150 °C, as shown in Figs. 3(a)–3(c). However, Fig. 3(d) indicates recrystallized Te after ALD deposition at 180 °C, resulting in

a substantial increase in grain boundaries, which led to the observed degradation in Dit. This trend is further supported by atomic force microscopy (AFM), which shows a gradual increase in mean surface roughness (Rq) with higher deposition temperatures. Raman spectroscopy of the Te regions revealed no significant shift in the vibrational mode peaks, but a reduction in the integrated intensity counts of the E<sub>2</sub> mode and broadening of its full width at half maximum (FWHM) were observed at elevated temperatures (see the supplementary material). The stable surface morphology of Te between 120 and 150 °C ALD temperatures, alongside a significant increase in D<sub>it</sub> of the SB capacitor, confirms that higher ALD temperatures promote deep trap site formation at the Te-ZrO2 interface. The notable reduction in Dit from SB to MB capacitors at 150 °C further indicates that these trap sites are particularly concentrated at Te grain boundaries. Additionally, in the MB capacitor, as the ZrO2 ALD temperature increased from 120 to 150 °C, Dit increased by approximately  $2.7 \times 10^{12}$  states/cm<sup>2</sup>·eV. This increase is attributed to the formation of additional interface trap sites due to the higher ALD temperature, even after minimizing the influence of grain boundaries.

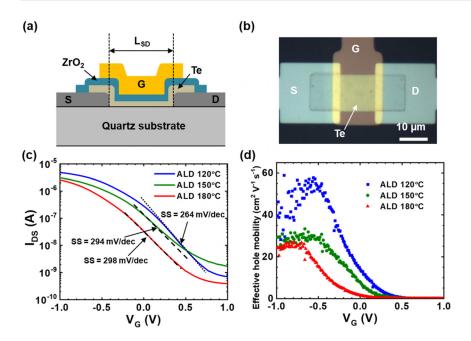

To assess the impact of Dit on FET performance, we fabricated FETs using the same process as the capacitors, as shown in Fig. 4(a). The devices feature a metal (Rh) contact-first scheme for the source and drain, an 8 nm-thick Te channel, a 10 nm-thick ALD ZrO2 gate dielectric, and Ti/Au gate electrodes. Figure 4(b) shows the fabricated FET with a Te channel width and length of 12  $\mu$ m each. Figure 4(c) presents the  $I_{DS}$ – $V_G$  characteristics at  $V_{DS}$  =  $-0.1\,V$  for the fabricated FETs. Devices with ZrO<sub>2</sub> gate oxide deposited at ALD temperatures of 120, 150, and 180 °C exhibited subthreshold swings (SSs) of 264, 294, and 298 mV/dec, respectively, as illustrated by the steepest slope in Fig. 4(c). The corresponding maximum effective hole mobilities vs V<sub>G</sub> were extracted to be 59, 33, and 27 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively, as shown in Fig. 4(d). These results clearly demonstrate a direct correlation between D<sub>it</sub> and device performance. However, the fabrication process in this study primarily focused on achieving a clean Te-ZrO2 interface, and the Te/source-drain contact scheme was not optimized. Consequently, the SS increased by approximately  $\sim$ 160 mV/dec compared to previous

FIG. 3. (a) Optical image and AFM morphology scan of the as-deposited Te after crystallization in the capacitor. (b)–(d) Optical images and AFM scans of the Te region in capacitors with ZrO<sub>2</sub> ALD temperatures of 120, 150, and 180 °C, respectively.

FIG. 4. (a) Cross-sectional schematic of the Te FET device structure and the measurement setup used for I–V measurements. (b) An optical microscope image of the FET with ZrO $_2$  gate oxide deposited at an ALD temperature of 120 °C. (c)  $I_{DS}\!\!-\!\!V_G$  characteristics of Te FETs with channel dimensions of  $12~\mu m \times 12~\mu m$  at ZrO $_2$  deposition temperatures of 120, 150, and 180 °C. (d) Effective hole mobility of FETs as a function of  $V_G$ .

reports.<sup>6</sup> Future improvements in Te-FET performance can be achieved by optimizing the device fabrication process, particularly developing optimal contacts for Te devices.

In conclusion,  $D_{it}$  of Te capacitors with ALD-deposited  $ZrO_2$  gate dielectric was extracted from the C–V and  $G/\omega$ -f characterization as a function of ALD deposition temperature. Te capacitors were fabricated in both SB and MB types, and the lowest  $D_{it}$  value, calculated using the conductance method, was found to be  $5\times10^{12}$  states/cm²-eV for the MB capacitor with  $ZrO_2$  deposited at  $120\,^{\circ}C$ , where the influence of Te grain boundaries was minimized. As the  $ZrO_2$  ALD deposition temperature increased up to  $180\,^{\circ}C$ ,  $D_{it}$  showed a notable increase, revealing a rise in grain boundary density due to Te

recrystallization. Increase in the ALD temperature led to the generation of deep trap sites at the Te–ZrO $_2$  interface. Likewise, Te FETs fabricated under the same conditions exhibited degradation in SS and effective hole mobility with increasing ZrO $_2$  deposition temperature, confirming a strong correlation with D $_{\rm it}$ . This work highlights the importance of defect minimized interface for enhancing scaled Te transistors in future technologies.

See the supplementary material for room temperature C–V characteristics and  $G/\varpi$  vs frequency plots of single and multi-bridged Te capacitors at various ZrO $_2$  ALD temperatures, and Raman spectra of the Te regions within the capacitors.

This work was supported by Samsung. Tellurium deposition and crystallization were performed in the Electronic Materials (EMAT) laboratories, supported by the U.S. Department of Energy, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division under contract no. DE-AC02-05Ch11231.

# **AUTHOR DECLARATIONS**

#### **Conflict of Interest**

The authors have no conflicts to disclose.

#### **Author Contributions**

Kyeong-Jae Byeon: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Writing - original draft (equal); Writing - review & editing (equal). I. K. M. Reaz Rahman: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Writing - original draft (equal); Writing - review & editing (equal). Inha Kim: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Project administration (equal); Writing - original draft (equal); Writing - review & editing (equal). Howoo Park: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Writing - original draft (equal); Writing - review & editing (equal). Ali Javey: Conceptualization (equal); Data curation (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Supervision (equal); Writing - original draft (equal); Writing - review & editing (equal).

## DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **REFERENCES**

- <sup>1</sup>J. Qiao, Y. Pan, F. Yang, C. Wang, Y. Chai, and W. Ji, Sci. Bull. **63**, 159 (2018).

- <sup>2</sup>Z. Shi, R. Cao, K. Khan, A. K. Tareen, X. Liu, W. Liang, Y. Zhang, C. Ma, Z. Guo, X. Luo, and H. Zhang, Nano-Micro Lett. 12, 99 (2020).

- <sup>3</sup>J. Zha, D. Dong, H. Huang, Y. Xia, J. Tong, H. Liu, H. P. Chan, J. C. Ho, C. Zhao, Y. Chai, and C. Tan, Adv. Mater. 36, 2408969 (2024).

- <sup>4</sup>Y. Yang, M. Xu, S. Jia, B. Wang, L. Xu, X. Wang, H. Liu, Y. Liu, Y. Guo, L. Wang, S. Duan, K. Liu, M. Zhu, J. Pei, W. Duan, D. Liu, and H. Li, Nat. Commun. 12, 6081 (2021).

- <sup>5</sup>C. Zhao, H. Batiz, B. Yasar, H. Kim, W. Ji, M. C. Scott, D. C. Chrzan, and A. Javey, Adv. Mater. 33, 2100860 (2021).

- <sup>6</sup>C. Zhao, C. Tan, D.-H. Lien, X. Song, M. Amani, M. Hettick, H. Y. Y. Nyein, Z. Yuan, L. Li, M. C. Scott, and A. Javey, Nat. Nanotechnol. 15, 53 (2020).

- 7J. Zha, J. Tong, H. Huang, Y. Xia, D. Dong, and C. Tan, Appl. Phys. Lett. 125, 070504 (2024).

- <sup>8</sup>L. Li, G. Zhang, M. Younis, T. Luo, L. Yang, W. Jin, H. Wu, B. Xiao, W. Zhang, and H. Chang, ACS Appl. Electron. Mater. 6, 2161 (2024).

- <sup>9</sup>C. Zhao, L. Hurtado, and A. Javey, Appl. Phys. Lett. 117, 192104 (2020).

- <sup>10</sup>R. Dutton and R. Muller, Thin Solid Films 11, 229 (1972).

- <sup>11</sup>Y.-C. Byun, J.-G. Lee, X. Meng, J. S. Lee, A. T. Lucero, S. J. Kim, C. D. Young, M. J. Kim, and J. Kim, Appl. Phys. Lett. 111, 082905 (2017).

- <sup>12</sup>M. Reinke, Y. Kuzminykh, and P. Hoffmann, Chem. Mater. 27, 1604 (2015).

- <sup>13</sup>M. Leskelä and M. Ritala, Thin Solid Films **409**, 138 (2002).

- D. M. Hausmann, E. Kim, J. Becker, and R. G. Gordon, Chem. Mater. 14, 4350 (2002).

N. Huby, S. Ferrari, E. Guziewicz, M. Godlewski, and V. Osinniy, Appl. Phys. Lett. 92, 023502 (2008).

- <sup>16</sup>K. Okuyama and Y. Kumagai, J. Appl. Phys. **46**, 1473 (1975).

- <sup>17</sup>C. M. Smyth, G. Zhou, A. T. Barton, R. M. Wallace, and C. L. Hinkle, Adv. Mater. Interfaces 8, 2002050 (2021).

- <sup>18</sup>X. Wang, S. K. Ghosh, M. Afshar-Mohajer, H. Zhou, Y. Liu, X. Han, J. Cai, M. Zou, and X. Meng, J. Mater. Res. 35, 804 (2020).

- <sup>19</sup>A. Zavabeti, P. Aukarasereenont, H. Tuohey, N. Syed, A. Jannat, A. Elbourne, K. A. Messalea, B. Y. Zhang, B. J. Murdoch, J. G. Partridge, and M. Wurdack, Nat. Electron. 4, 277 (2021).

- <sup>20</sup> A. Liu, Y. S. Kim, M. G. Kim, Y. Reo, T. Zou, T. Choi, S. Bai, H. Zhu, and Y. Y. Noh, Nature 629, 798 (2024).

- <sup>21</sup>S. Hlali, N. Hizem, and A. Kalboussi, J. Comput. Electron. 15, 1340 (2016).

- <sup>22</sup>I. Hussain, M. Y. Soomro, N. Bano, O. Nur, and M. Willander, J. Appl. Phys. 112, 064506 (2012).

- <sup>23</sup>R. Suzuki, N. Taoka, M. Yokoyama, S. Lee, S. H. Kim, T. Hoshii, T. Yasuda, W. Jevasuwan, T. Maeda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, Appl. Phys. Lett. 100, 132906 (2012).

- <sup>24</sup>S. M. Pazos, F. L. Aguirre, K. Tang, P. McIntyre, and F. Palumbo, J. Appl. Phys. 124, 224102 (2018).

- <sup>25</sup>V. Djara, K. Cherkaoui, M. Schmidt, S. Monaghan, E. O'Connor, I. M. Povey, D. O'Connell, M. E. Pemble, and P. K. Hurley, IEEE Trans. Electron Devices 59, 1084 (2012).

- <sup>26</sup>K. Takei, R. Kapadia, H. Fang, E. Plis, S. Krishna, and A. Javey, Appl. Phys. Lett. **102**, 153513 (2013).

- <sup>27</sup>E. H. Nicollian and A. Goetzberger, Appl. Phys. Lett. **10**, 60 (1967).

- <sup>28</sup>K. Martens, C. O. Chui, G. Brammertz, B. De Jaeger, D. Kuzum, M. Meuris, M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, IEEE Trans. Electron Devices 55, 547 (2008).

- <sup>29</sup>T. Balasubramaniam, S. K. Narayandass, and D. Mangalaraj, Bull. Mater. Sci. 20, 79 (1997).