news & views

### NANOELECTRONICS

# **Towards flexible CMOS circuits**

Tellurium thin films evaporated at cryogenic temperatures facilitate the realization of high performance wafer-scale flexible *p*-type field-effect transistors and various types of logic gates.

## Seungjun Chung and Takhee Lee

omplementary metal oxide semiconductor (CMOS) technology has been at the core of applications in digital logic circuits, communication, signal sensing and memory chips<sup>1,2</sup>. CMOS is a type of metal-oxide-semiconductor field-effect transistor (MOSFET) technology that uses symmetrical pairs of p-type and n-type MOSFETs for logic functions. Specifically, its attractive advantages over unipolar transistors such as low static power consumption, high noise immunity and logic swing output have tremendously accelerated the growth of today's digital world<sup>2</sup>. However, for some applications such as wearable electronics, the technological demands towards physical flexibility and robustness of large-area electronic devices go beyond conventional siliconbased CMOS technology<sup>1,3,4</sup>. From the perspective of flexibility, the deposition of semiconductors must be performed at low temperatures maintaining their high electrical performance, energy efficiency and large-scale integration capability.

In the past few decades, various types of semiconductors and flexible substrates have been used to realize low-temperature processed field-effect transistors (FETs). In particular, amorphous metal-oxide n-type semiconductors<sup>4</sup>, such as amorphous InGaZnO (a-IGZO), ZnO, IZO and InO<sub>x</sub> deposited at plastic-compatible temperatures (<200 °C) or at room-temperature with the assistance of photochemical activation have shown suitable electrical performance for active-matrix electronics, including displays and sensor arrays5. Although lowtemperature processed Cu<sub>v</sub>O, NiO<sub>v</sub> and SnO have emerged as p-type oxide-based materials<sup>6</sup>, their intrinsically lower electrical performance including a hole mobility of  $\sim 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  compared to that of n-type semiconductors is a critical bottleneck for realizing high performance and energyefficient CMOS applications. The discovery of low-dimensional p-type semiconductors such as carbon nanotubes, nanowirebased materials and two-dimensional (2D) transition metal dichalcogenides. has ushered in a new class of alternative

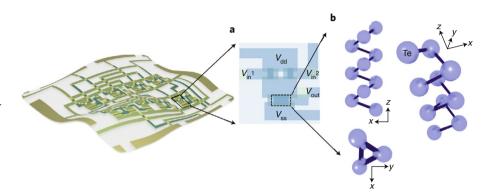

**Fig. 1** A schematic image showing a flexible computational circuit of 2-bit multiplier with 39 Te field-effect transistors. a, Top-view schematic image of a NAND gate based on a *p*-MOS inverter. For the MOS fabrication, Ti/Au (2 nm/18 nm) gate electrodes were deposited by e-beam evaporation. On the gate electrodes, the  $ZrO_2$  dielectric layer was deposited by atomic layer deposition. For the channel layer, 8 nm-thick Te thin films were deposited onto a -80 °C substrate, and then 30 nm-thick Ni electrodes were deposited by e-beam evaporation as metal contacts. Javey and co-workers<sup>9</sup> showed feasibility to realize high performance *p*-MOS by conventional evaporation systems in plastic-compatible temperatures. Here,  $V_{inr}$ ,  $V_{outr}$ ,  $V_{ddr}$  and  $V_{ss}$  are the input voltage, output voltage, positive supply voltage and negative supply voltage (or ground), respectively. **b**, Perspective, top and side views of the crystal structure of Te, which is composed of covalently-bonded atoms in a helical chain along a single axis.

flexible p-type materials with tunable electrical properties<sup>3,7</sup>. However, as far as the use of low-dimensional materials is concerned, further improvements towards large-scale integration with high device yield are required. Although many research groups have been intensively working on high performance p-type organic semiconducting devices owing to lowtemperature processing advantages<sup>8</sup>, their potential applications are still limited due to intrinsically inferior electrical performance and environmental stability.

Writing in *Nature Nanotechnology*, Javey and co-workers have reported tellurium thin films obtained via thermal evaporation at cryogenic temperatures that can facilitate the realization of high performance waferscale flexible p-type FETs and various types of logic<sup>9</sup>.

Previous reports have already demonstrated that single-crystalline Te nanostructures exhibit excellent hole mobility of a few hundred cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (ref. <sup>10</sup>), however the realization of Te-based largearea FETs at plastic-compatible temperatures remains challenging. Specifically, because the domain size of Te films largely determines their electrical performance including hole mobility, further optimization of the Te film growth conditions is required. To address this issue, thermal evaporation at cryogenic temperatures was employed to improve the Te film quality, especially for achieving larger domains. The authors have also systematically investigated the effects of the evaporation temperature on the domain size and the electrical performance. As a result, FETs based on Te films evaporated at a substrate temperature of -80 °C exhibit an effective hole mobility of ~35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, an on/off ratio of ~104 and a subthreshold swing of 108 mV dec<sup>-1</sup> measured at room temperature. This desirable p-type behaviour is primarily attributed to an increased domain size, which was not observed for Te films deposited at higher temperatures. Interestingly, the

effective hole mobilities extracted for the temperature range 77-300 K show no temperature dependence indicating that this parameter is critically limited by the grain boundary in the Te films. Therefore, the reported p-type Te films together with the mature low-temperature processed n-type semiconductors may offer a potential solution for realizing high performance large area flexible CMOS platforms. To illustrate the potential of the presented concept, Javey and co-workers show the realization of various flexible logic gates and computational circuits, such as an inverter, NAND gate (Fig. 1), full adder and multiplier composed of dozens of transistors through conventional semiconductor processing9. These demonstrations were not possible with other emerging p-type candidates. Furthermore, the authors construct monolithic three-dimensional (3D) integrated circuits and back-end-ofline electronics achieving high density integration.

In the future, more feasible strategies enabling the realization of improved flexible complementary ICs will be needed for even higher integration density, better deviceto-device uniformity, high operating speed and low power consumption. Currently, the deposition of Te, which takes place at -80 °C, is not industrially compatible. However, this work clearly indicates that the approach of employing thermally evaporated Te films is beneficial in terms of providing sufficient electrical performance to match the available n-type semiconductors. In addition, existing facilities for fabricating conventional silicon-based electronics can be utilized with high reliability in batch manufacturing, which allows the realization of complex computational circuits and monolithic 3D integrated circuits based on CMOS technology with minimized additional costs. For tellurium, to qualify as a promising p-type material, further studies should focus on ensuring higher quality (for example, crystallinity, domain size and impurities) of thermally evaporated Te thin films and better CMOS compatibility of the deposition process (for example, substrate temperature). If these requirements can

be met, this approach could accelerate the coming of the Internet of Things world connected by energy-efficient flexible 3D electronics.

#### Seungjun Chung<sup>1</sup> and Takhee Lee<sup>D<sup>2</sup></sup>

<sup>1</sup>Photo-Electronic Hybrids Research Center, Korea Institute of Science and Technology, Seoul, Korea. <sup>2</sup>Department of Physics and Astronomy, Seoul National University, Seoul, Korea. e-mail: seungjun@kist.re.kr; tlee@snu.ac.kr

#### Published online: 16 December 2019

#### https://doi.org/10.1038/s41565-019-0596-6

#### References

- 1. Myny, K. Nat. Electron. 1, 30-39 (2018).

- 2. Hussain, A. M. & Hussain, M. M. Adv. Mater. 28, 4219–4249 (2016).

- 3. Tang, J. et al. Nat. Electron. 1, 191-196 (2018).

- Park, J. W., Kang, B. H. & Kim, H. J. Adv. Func. Mater. https://doi. org/10.1002/adfm.201904632 (2019).

- 5. Kim, Y.-H. et al. Nature 489, 128-132 (2012).

- Wang, Z., Nayak, P. K., Caraveo-Frescas, J. A. & Alshareef, H. N. Adv. Mater. 28, 3831–3892 (2016).

- Manzeli, S., Ovchinnikov, D., Pasquier, D., Yazyev, O. V. & Kis, A. Nat. Rev. Mater. 2, 17033 (2017).

- 8. Giri, G. et al. Nature 480, 504-508 (2011).

- Zhao, C. et al. Nat. Nanotechnol. https://doi.org/10.1038/s41565-019-0585-9 (2019).

- 10. Wang, Y. et al. Nat. Electron. 1, 228-236 (2018).