## **Evaporated tellurium thin films for p-type field-effect transistors and circuits**

Chunsong Zhao<sup>1,2,3,5</sup>, Chaoliang Tan<sup>1,2,5</sup>, Der-Hsien Lien<sup>1,2</sup>, Xiaohui Song<sup>3,4</sup>, Matin Amani<sup>1,2</sup>, Mark Hettick<sup>1,2</sup>, Hnin Yin Yin Nyein<sup>1,2,3</sup>, Zhen Yuan<sup>1,2</sup>, Lu Li<sup>1,2</sup>, Mary C. Scott<sup>3,4</sup> and Ali Javey<sup>1,2,4</sup>

There is an emerging need for semiconductors that can be processed at near ambient temperature with high mobility and device performance. Although multiple n-type options have been identified, the development of their p-type counterparts remains limited. Here, we report the realization of tellurium thin films through thermal evaporation at cryogenic temperatures for fabrication of high-performance wafer-scale p-type field-effect transistors. We achieve an effective hole mobility of ~35 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, on/off current ratio of ~10<sup>4</sup> and subthreshold swing of 108 mV dec<sup>-1</sup> on an 8-nm-thick film. High-performance tellurium p-type field-effect transistors are fabricated on a wide range of substrates including glass and plastic, further demonstrating the broad applicability of this material. Significantly, three-dimensional circuits are demonstrated by integrating multi-layered transistors on a single chip using sequential lithography, deposition and lift-off processes. Finally, various functional logic gates and circuits are demonstrated.

xploring semiconductor thin films grown at low temperature (400 °C or lower) with high mobility and device performance is of great importance for a number of applications including transparent/flexible electronics and monolithic three-dimensional (3D) complementary metal-oxide-semiconductor (CMOS) architectures<sup>1-3</sup>. Specifically, the processing temperature for constructing monolithic 3D CMOS, where multiple active circuit layers are stacked on top of each other, needs to be maintained below 300-400 °C to prevent degradation of the underlying devices and interconnects, and it needs to be even lower (below 200°C or even less) for flexible electronics because of the low glass transition temperatures of polymer substrates (for example, the maximum stable temperature of polyethylene terephthalate (PET) is around 150 °C)4-6. Multiple n-type material systems with respectable electron mobility of the order of 10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, such as a-IGZO (amorphous indium gallium zinc oxide), zinc oxide, indium oxide, cadmium sulfide and cadmium selenide1,7-10, have been identified, but the development of their p-type counterparts has been limited despite many years of effort. Widely explored low-temperature processing p-type thin films are amorphous silicon, metal oxides (for example, copper oxide, nickel oxide and tin oxide), organic compounds/polymers and polycrystalline germanium (Ge)<sup>2,3,11,12</sup>. Among them, amorphous silicon, metal oxides and organic compounds/polymers normally exhibit low hole mobilities of the order of 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> or even less<sup>2,5,11,13,14</sup>. Vapourphase-deposited polycrystalline germanium films give high hole mobility up to 110 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. However, their applications are limited by the need for sequential annealing and/or metal catalysts to induce the crystallization<sup>12</sup>. Alternatively, carbon nanotubes (CNTs) have been explored as a promising p-type nanomaterial and solution-processed CNT-based networks exhibit hole mobility of up to tens of cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. However, their nanoscale processing remains a concern<sup>6,15–18</sup>. In addition, layer transfer of high-temperature grown materials such as chemical-vapour-deposition-grown CNT arrays and III-V compound semiconductors has also been explored, but large-scale processing necessary is still a challenge<sup>4,19,20</sup>.

Recently, single-crystalline tellurium (Te) nanostructures with a bandgap energy of  $E_g = 0.31 \text{ eV}$  have been shown to exhibit high hole mobilities up to 707 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, but their large-scale processing is challenging, which hence limits their applications<sup>21,22</sup>. On the other hand, large-scale polycrystalline Te thin films with tens of nanometre thickness prepared by thermal evaporation were studied in the 1960-70s<sup>23-25</sup>. Material quality (that is, grain size) and transport properties (that is, carrier mobility) of the evaporated Te films were shown to be tuned by substrate temperature<sup>24</sup>, nucleation layer<sup>26,27</sup> and deposition rate<sup>26,27</sup>. Specifically, the grain size strongly depends on the deposition temperature with the maximum size obtained at cryogenic temperatures<sup>24</sup>. Optimized evaporated Te films have shown high Hall mobility (up to a few hundred cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>)<sup>23,24</sup>. However, high-performance field-effect transistors (FETs) with good switching characteristics have still not been achieved<sup>23,25</sup>. Here we report ultrathin Te thin films, which are deposited by thermal evaporation at low temperature (-80 °C), for fabrication of highperformance wafer-scale p-FETs, logic gates and computational circuits. The low processing temperature of Te p-FETs makes them compatible with a wide range of substrates, including silicon integrated circuits, glass and plastics.

#### Te thin-film synthesis and characterization

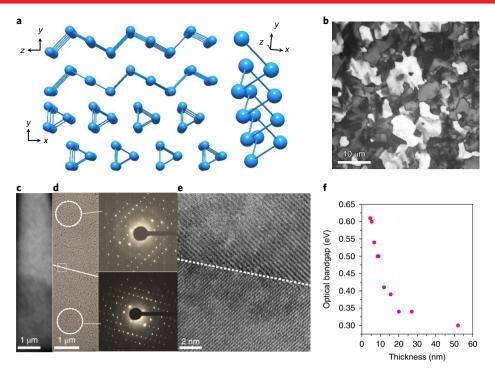

Te is composed of covalently bonded atoms sequenced in a helical chain along a single axis, with chains packed in a hexagonal array via van der Waals force (Fig. 1a). Domains with different contrast were observed under polarized light microscopy. The domains correspond to the arrays of aligned Te molecular chains, acting like wire grid polarizers, with absorption dependent on the angle between the light polarization and the array (polarized transmission measurements of different domains are shown in Supplementary Fig. 1). From X-ray diffraction (XRD) analysis, the absence of the (003) peak indicates that Te molecular chains are aligned in the plane of the substrate (Supplementary Fig. 2a). To further confirm the crystal structure of different domains, transmission electron

<sup>&</sup>lt;sup>1</sup>Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA, USA. <sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA, USA. <sup>3</sup>Department of Materials Science and Engineering, University of California at Berkeley, Berkeley, CA, USA.

$<sup>^4</sup>$ The Molecular Foundry, Lawrence Berkeley National Laboratory, Berkeley, CA, USA.  $^5$ These authors contributed equally: Chunsong Zhao, Chaoliang Tan.

<sup>\*</sup>e-mail: ajavey@eecs.berkeley.edu

ARTICLES NATURE NANOTECHNOLOGY

**Fig. 1 | Characterization of Te thin films evaporated with a substrate temperature of —80 °C. a**, Crystal structure of Te. **b**, Polarized light microscopy image of a Te film (9 nm). **c**, Enlarged optical image of a Te film (9 nm) on SiO<sub>2</sub> TEM grid, depicting a grain boundary. **d**, The low magnification TEM image of the Te film (9 nm) in **c**. The dashed line indicates the grain boundary. Insets are the corresponding selected-area electron diffraction patterns. **e**, HRTEM image of the same film at the boundary area. **f**, Thickness-dependent optical bandgap of Te thin films.

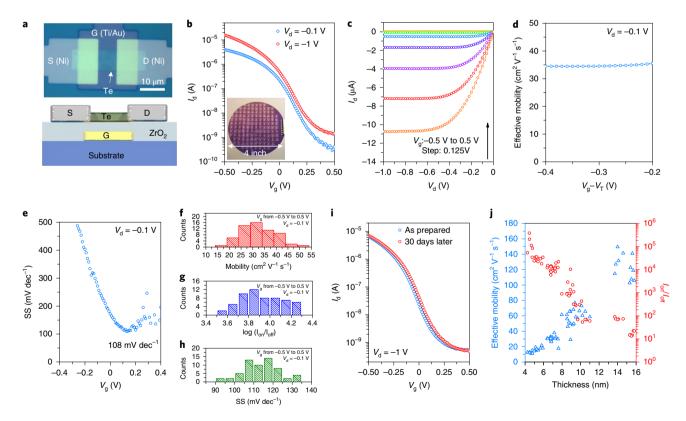

**Fig. 2 | FETs based on Te evaporated with a substrate temperature of -80 °C. a,** Optical image of a typical Te FET and schematic diagram of the device structure. **b,**  $I_d$ – $V_g$  transfer curves of the Te transistor (8 nm) in **a.** Inset: photograph of wafer-scale (4-inch) Te FETs. **c,**  $I_d$ – $V_d$  output characteristics of the same device as shown in **b. d,e**, Effective mobility (**d**) and SS (**e**) derived from the  $I_d$ – $V_g$  curves shown in **b. f-h**, The statistical distribution of effective mobility (**f**), log ( $I_{on}$ / $I_{off}$ ) (**g**) and SS (**h**) for 60 individual transistors from different points on the wafer. **i,**  $I_d$ – $V_g$  characteristic of a Te FET measured immediately and 30 days after fabrication. **j**, Thickness-dependent effective mobility (blue) and on/off current ratio (red) for Te FETs. Note that the thicknesses of Te film were measured by AFM.

**ARTICLES**

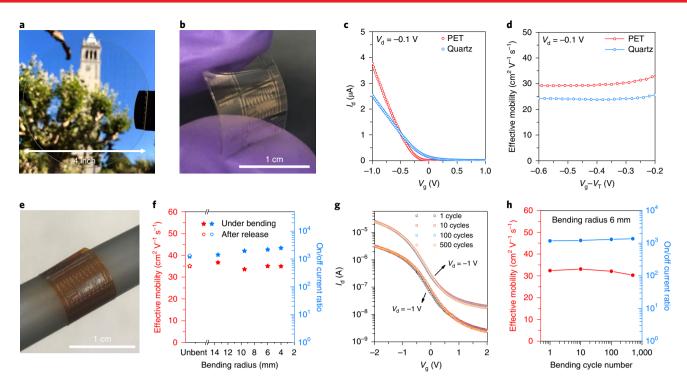

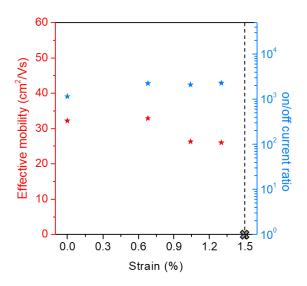

**Fig. 3** | **Flexible and transparent FETs based on Te evaporated with a substrate temperature of -80 °C. <b>a,b**, Photograph of Te FETs fabricated on 4-inch quartz wafer (**a**) and PET substrate (**b**). **c**,  $I_d - V_g$  transfer curves for evaporated Te FETs on quartz and PET substrates. **d**, Effective mobility of 8-nm-thick Te FETs on quartz and PET substrates. **e**, Photograph of Te FETs on Kapton substrate while bent (the thickness of the Kapton substrate is 50  $\mu$ m). **f**, Effective mobility and on/off current ratio of Te FET (8 nm) on Kapton substrate under different bending radius. **g**,  $I_d - V_g$  transfer curves of the Te transistor (8 nm) on PET substrate after different bending cycles. **h**, Effective mobility and on/off current ratio of Te FET (8 nm) on Kapton substrate after different bending cycles.

microscopy (TEM) was performed (Fig. 1c). The selected-area electron diffraction patterns of two regions with different contrast show single-crystalline diffraction spots with different orientations, suggesting that both regions are single-crystal-like domains (Fig. 1d). The high-resolution (HR)TEM image clearly shows the grain boundary of the two domains (Fig. 1e). Note that defects can be observed from the HRTEM image (Supplementary Fig. 2b), suggesting that domains are not perfect single crystals.

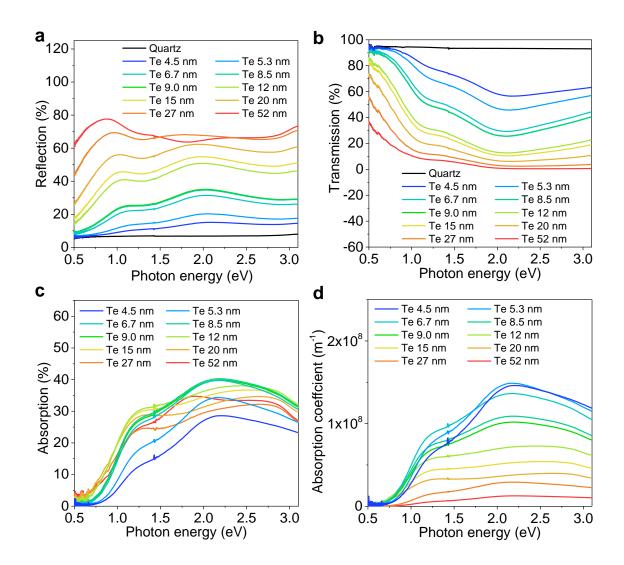

We first investigate the thickness effect on the domain size of Te films evaporated with a substrate temperature of  $-80\,^{\circ}$ C. Te films with thickness varying from 8 to 30 nm were analysed using the polarized light microscope. We observed minimal thickness dependence for the domain size for the studied thickness of 8 to 30 nm (Supplementary Fig. 3). The extracted optical bandgap from the absorption measurements shows a thickness-dependent behaviour, from  $0.3\,\mathrm{eV}$  for bulk to  $0.6\,\mathrm{eV}$  for 4.5-nm-thick evaporated Te films (Fig. 1e and Supplementary Fig. 4) due to the quantum confinement effect. Our results are consistent with the previously reported calculations and experimental results on single-crystalline Te layers 29.

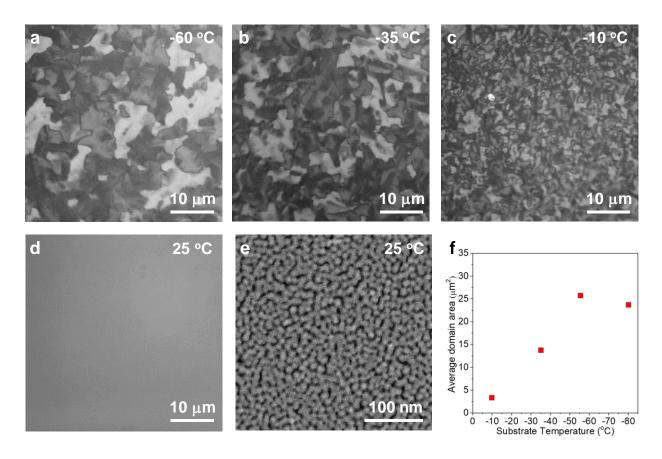

We also found that the substrate temperature for evaporation has a significant impact on the Te film quality. When the substrate temperature decreases from  $-10\,^{\circ}\text{C}$  to  $-60\,^{\circ}\text{C}$ , the average area of domains monotonically increases from  $\sim 3\,\mu\text{m}^2$  to  $\sim 25\,\mu\text{m}^2$  (Supplementary Fig. 5). Below  $-60\,^{\circ}\text{C}$ , the domain size does not change with further decrease of temperature (Supplementary Fig. 5f). At room temperature (the substrate temperature of 25  $^{\circ}\text{C}$ ), the film is not continuous and instead consists of small nanoparticles (Supplementary Fig. 5e).

#### **Electrical characterization of Te FETs**

The evaporation temperature effect on the device performance of Te FETs is explored given its significant impact on the domain size.

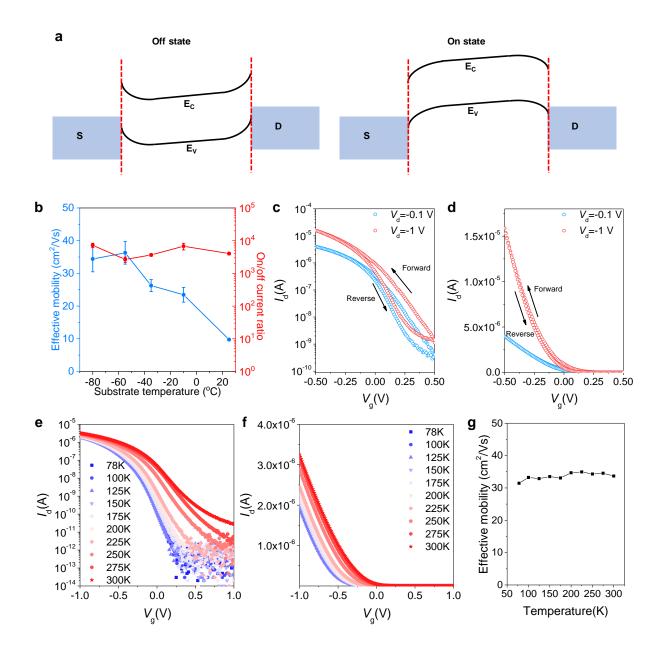

We fabricate FETs based on Te films (8 nm) evaporated at different temperatures from 25 °C to -80 °C. The device structure consists of a Ti/Au local bottom gate, a 5-nm  $\rm ZrO_2$  (dielectric constant  $\approx$  16) gate dielectric (Fig. 2a) and Ni as source/drain metal contacts. The energy band diagram of the device is shown in Supplementary Fig. 6a. As shown in Supplementary Fig. 6b, the effective mobility decreases from 35 to  $10\,\rm cm^2V^{-1}\,s^{-1}$  with the increase of the substrate temperature. The higher mobility for FETs based on Te thin film evaporated at  $-80\,^{\circ}\rm C$  can mainly be attributed to larger domain size, compared to those deposited at higher temperatures  $^{24}$ . To this end, we use Te films evaporated with a substrate temperature of  $-80\,^{\circ}\rm C$  for subsequent device and circuit fabrication.

Uniform Te FETs can be easily fabricated at wafer scale given the simplicity of the Te deposition (Fig. 2b, inset). The Te FET shows a typical p-type characteristic as shown in Fig. 2b,c. A hysteresis in the voltage sweep measurement is observed, which is a common behaviour for a thin-film device without encapsulation (Supplementary Fig. 6c,d). The transistor exhibits an effective hole mobility of ~35 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, on/off current ratio of ~10<sup>4</sup> and subthreshold swing (SS) of 108 mV dec-1 at room temperature (Fig. 2d,e). To study the uniformity of Te FETs, we randomly measured 60 devices on a wafer. The devices exhibit a narrow distribution in performance with standard deviation of  $32 \pm 7 \,\mathrm{cm^2 V^{-1} s^{-1}}$  in mobility,  $9,491 \pm 4,765$  in on/off current ratio and  $114 \pm 9$  mV dec<sup>-1</sup> in SS (Fig. 2f-h). Importantly, the performance of the Te FET did not show obvious degradation after leaving the device in ambient air without any encapsulation for 30 days (Fig. 2i). Temperaturedependent drain current  $(I_d)$ -gate voltage  $(V_g)$  transfer curves are measured to investigate the carrier scattering mechanisms (Supplementary Fig. 6e,f). The effective mobility is nearly independent of temperature from 77 K to 300 K (Supplementary Fig. 6g), suggesting that the mobility is limited by the grain boundary and ARTICLES NATURE NANOTECHNOLOGY

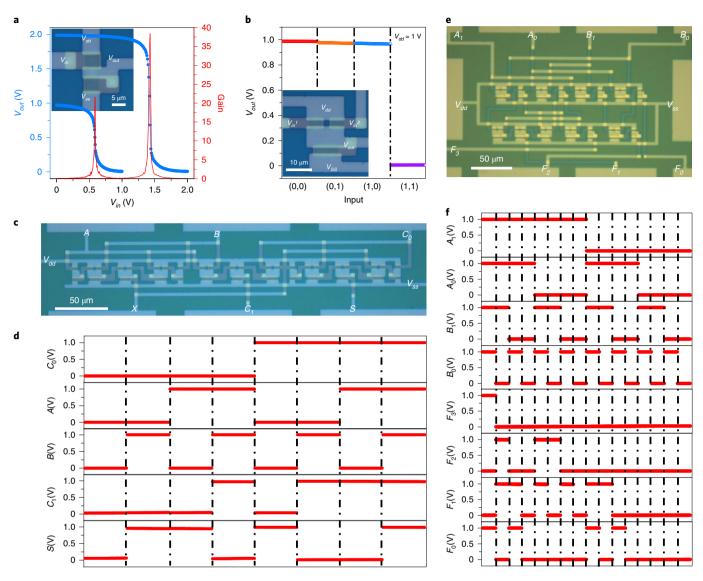

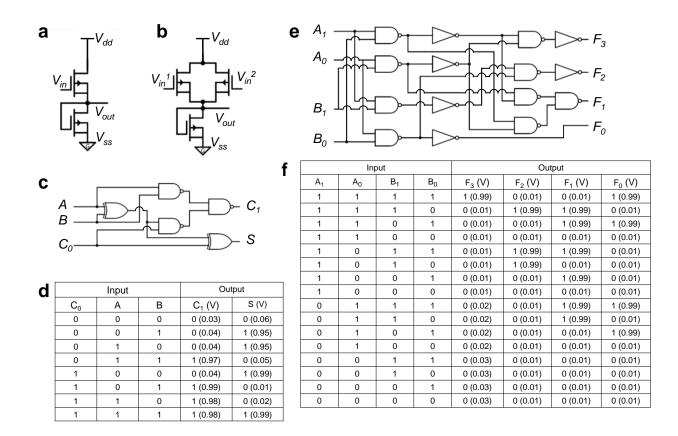

**Fig. 4 | Integrated circuits based on Te FETs. a,b**, Inverter (**a**) and NAND logic gate (**b**) performance. The inset shows an optical image of the device. **c,d**, Optical image (**c**) and output voltage (**d**) of a full-adder. **e,f**, Optical image (**e**) and output voltage (**f**) of a 2-bit multiplier. The supply voltage,  $V_{dd}$  was 1V for the NAND gate, full-adder and 2-bit multiplier. Different input and the corresponding output states are separated by black dashed lines in **d** and **f**. Circuit designs and the experimental truth table are shown in Supplementary Fig. 9.

surface roughness scattering<sup>22,30</sup>. In the future, it may be possible to further improve the mobility by increasing the domain size and reducing the surface roughness by optimizing the evaporation process.

We then investigated the thickness-dependent effective mobility and on/off current ratio, which are the key metrics for transistors (Fig. 2j). Here, we vary the channel thickness from 4 to 16 nm. Te FETs become open circuits at sub-4-nm thickness and the evaporated films were found not to be continuous. The on/off current ratio decreases from  $\sim\!10^5$  (4 nm Te) to  $\sim\!10$  (16 nm Te), which is probably due to the decrase of the bandgap of the Te channel, and electrostatic control is reduced as thickness increases. In contrast, the effective mobility increases with thickness monotonically from  $10\,\mathrm{cm^2V^{-1}\,s^{-1}}$  to  $140\,\mathrm{cm^2V^{-1}\,s^{-1}}$ . The monotonically increased mobility along with the film thickness could be attributed to the reduced effect of surface roughness scattering for thicker films, which is often observed in various material systems  $^{19,31}$ .

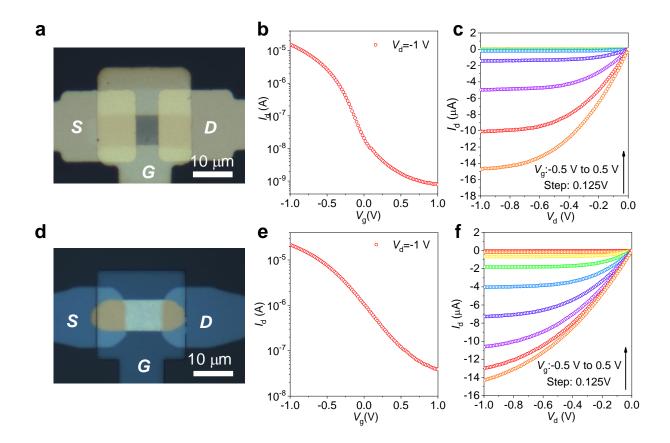

As a benefit of the low-temperature evaporation process, Te can be readily deposited on various substrates such as glass and plastic over large areas (Fig. 3a,b). We fabricated 8-nm-thick Te FETs on 4-inch quartz wafer and PET substrates with the same device structure shown in Fig. 2a. Te FETs on different substrates show similar hole mobilities (in the range of 25-35 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and onstate currents (Fig. 3c,d and Supplementary Fig. 7), suggesting that Te FETs can be used in broad applications, such as flexible and transparent electronics and displays<sup>32</sup>. We characterized the mechanical flexibility and operational stability of Te FETs on Kapton substrate. Fig. 3e shows a photograph of Te FETs on Kapton substrate when bent to a radius of 6 mm. The device mobility and on/off current ratio do not significantly change during bending up to a radius of 4 mm, corresponding to a tensile strain of 0.63% (Fig. 3f). A change in device performance is observed when strain is higher than 0.63%. The device becomes open circuit when strain reaches 1.5%, which is non-recoverable (Supplementary Fig. 8). Furthermore, the electrical properties of the device do not significantly change after multiple cycles (500) of bending at a radius of 6 mm, which corresponds to a strain of 0.42% (Fig. 3g,h).

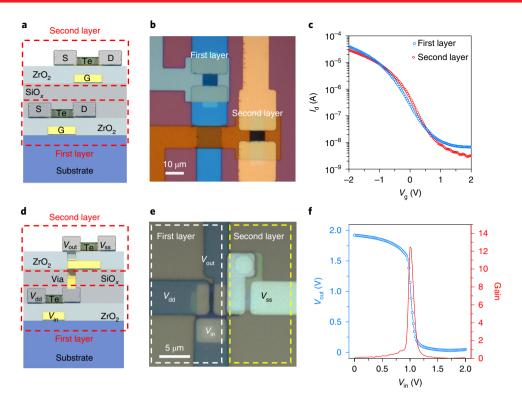

**Fig. 5 | Multi-layered Te FETs and 3D inverters. a-c**, A schematic diagram (**a**), optical image (**b**) and  $I_d$ - $V_g$  transfer curves ( $V_d$ =-1V) (**c**) of the two-layered transistor. The thickness of Te channels for both layers is 8 nm. **d-f**, A schematic diagram (**d**), optical image (**e**) and voltage transfer characteristic (**f**) of the 3D inverter based on Te FETs (with Te channels of 8 nm).

#### Logic gates and circuits based on Te devices

The high uniformity of Te FETs allows for fabrication of logic gates and computational circuits. Considering the trade-off between on/ off current ratio and mobility, 8-nm-thick Te FETs are selected as the building blocks. First, a p-type metal-oxide-semiconductor (p-MOS) inverter, the simplest logic gate, is constructed using two Te devices, acting as the driver and active load, respectively (Fig. 4a inset and Supplementary Fig. 9a). Fig. 4a shows typical voltage transfer curves with a gain of 22 and 38 at an operating voltage  $V_{\rm dd} = 1 \, \text{V}$  and  $V_{\rm dd} = 2 \, \text{V}$ , respectively. We also fabricated a NAND gate with a logically valid output (Fig. 4b and Supplementary Fig. 9b). The basic logic gates facilitate the design of more complex circuits. A full-adder is a key component of arithmetic logic units, with myriad applications such as encoders, decoders and binary calculation<sup>17</sup>. Functionally, a full-adder is aimed to add two one-bit numbers (A and B) and one carry number  $(C_0)$ , producing a two-bit sum (S)and new carry  $(C_1)$  as outputs. The Te FET based full-adder, which includes 9 NANDs and 4 inverters that are constructed from a total number of 35 transistors, is fabricated and shown in Fig. 4c. The fulladder functions properly with a maximum output voltage loss of 6% (Fig. 4c,d and Supplementary Fig. 9c,d). Therefore, we also fabricated a multiplier circuit to realize multiplication functions using 39 transistors. Functionally, four input terminals accept two 2-bit factors  $(A_1A_0 \text{ and } B_1B_0)$  and the output is a 4-bit product  $(F_3F_2F_1F_0)$ . The multiplication operation is achieved with a maximum output voltage loss of 3% (Fig. 4c,d and Supplementary Fig. 9e,f).

#### Demonstration of 3D monolithic circuits

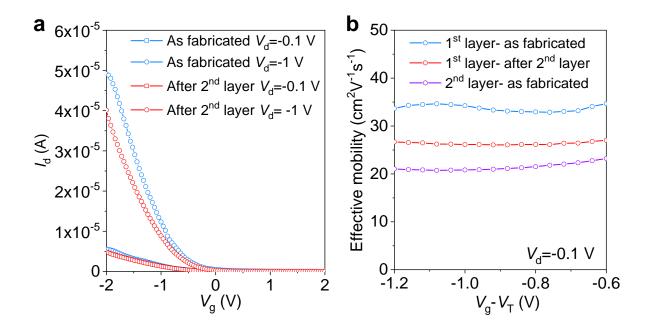

The performance of Te p-FETs is sufficient to enable the realization of complementary 3D monolithic ICs and back-end-of-line electronics when combined with the existing n-FETs such as *a*-IGZO<sup>1,4</sup>. Therefore, as a proof-of-concept, we fabricated multilayer transistors and logic gates based on Te p-FETs. Figure 5a,b show the

two-layer transistors fabricated using an evaporated SiO, isolation layer. The devices on the first and second layers show similar  $I_4$ –Vtransfer curves (Fig. 5c). Importantly, the electrical property of the first layer does not significantly change after the construction of the top layer given the low processing temperature used for all the fabrication steps (Supplementary Fig. 10). Note that a small threshold voltage  $(V_t)$  shift is observed. This shift is probably caused by a fixed charge in the intermediate oxide or at the semiconductor-oxide interface, which can be improved by moving to a more suitable insulation layer or a more optimized deposition technique. A 3D circuit, specifically, a two-layer inverter, is also demonstrated. The upper-layer transistor, acting as an active load, is vertically connected to the bottom-layer transistor acting as the driver (Fig. 5d,f). The 3D inverter accomplishes the desired NOT function with a gain of approximately 12 at a  $V_{dd} = 2 \text{ V}$  (Fig. 5f). These results demonstrate the practicality of Te p-FETs for monolithic 3D circuits.

#### **Conclusions**

We have demonstrated that evaporated Te thin films are an attractive material for p-FETs processed at low temperatures with important practical implications in monolithic 3D circuits, as well as flexible and transparent and/or large-area electronics. We believe that further improvements in the thin-film quality (for example, purity, crystallinity and surface smoothness) will enhance the device performance of Te FETs. Future integration of Te p-FETs with low-temperature n-type FETs, such as *a*-IGZO, can enable the construction of 3D CMOS circuits. Te p-FETs can also be implemented into back-end-of-line electronics with existing silicon CMOS circuits to further extend/enhance the system performance.

#### Online content

Any methods, additional references, Nature Research reporting summaries, source data, extended data, supplementary information,

ARTICLES NATURE NANOTECHNOLOGY

acknowledgements, peer review information; details of author contributions and competing interests; and statements of data and code availability are available at https://doi.org/10.1038/s41565-019-0585-9.

Received: 26 March 2019; Accepted: 4 November 2019; Published online: 16 December 2019

#### References

- Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* 432, 488–492 (2004).

- Wang, Z., Nayak, P. K., Caraveo-Frescas, J. A. & Alshareef, H. N. Recent developments in p-type oxide semiconductor materials and devices. *Adv. Mater.* 28, 3831–3892 (2016).

- Kim, M.-G., Kanatzidis, M. G., Facchetti, A. & Marks, T. J. Low-temperature fabrication of high-performance metal oxide thin-film electronics via combustion processing. *Nat. Mater.* 10, 382–388 (2011).

- Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. *Nature* 547, 74–78 (2017).

- Kwon, J. et al. Three-dimensional monolithic integration in flexible printed organic transistors. Nat. Commun. 10, 54 (2019).

- Chen, H., Cao, Y., Zhang, J. & Zhou, C. Large-scale complementary macroelectronics using hybrid integration of carbon nanotubes and IGZO thin-film transistors. *Nat. Commun.* 5, 4097 (2014).

- Rembert, T., Battaglia, C., Anders, A. & Javey, A. Room temperature oxide deposition approach to fully transparent, all-oxide thin-film transistors. *Adv. Mater.* 27, 6090–6095 (2015).

- Yeom, H.-I., Ko, J. B., Mun, G. & Park, S.-H. K. High mobility polycrystalline indium oxide thin-film transistors by means of plasma-enhanced atomic layer deposition. J. Mater. Chem. C. 4, 6873–6880 (2016).

- Martinez-Landeros, V. H. et al. Low-temperature thin film transistors based on pulsed laser deposited CdS active layers. Semicond. Sci. Tech. 34, 025008(2018).

- Stinner, F. S. et al. Flexible, high-speed CdSe nanocrystal integrated circuits. Nano Lett. 15, 7155–7160 (2015).

- 11. Sirringhaus, H. 25th Anniversary Article: Organic field-effect transistors: the path beyond amorphous silicon. *Adv. Mater.* **26**, 1319–1335 (2014).

- Shahrjerdi, D., Hekmatshoar, B., Mohajerzadeh, S., Khakifirooz, A. & Robertson, M. High mobility poly-Ge thin-film transistors fabricated on flexible plastic substrates at temperatures below 130 °C. *J. Electron. Mater.* 33, 353–357 (2004).

- Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: a review of recent advances. Adv. Mater. 24, 2945–2986 (2012).

- 14. Powell, M. J. The physics of amorphous-silicon thin-film transistors. *IEEE Trans. Electron Devices* **36**, 2753–2763 (1989).

- Geier, M. L. et al. Solution-processed carbon nanotube thin-film complementary static random access memory. *Nat. Nanotechnol.* 10, 944–948 (2015).

- Park, H. et al. High-density integration of carbon nanotubes via chemical self-assembly. Nat. Nanotechnol. 7, 787–791 (2012).

- Chen, B. et al. Highly uniform carbon nanotube field-effect transistors and medium scale integrated circuits. Nano Lett. 16, 5120–5128 (2016).

- Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nat. Nanotechnol. 8, 180–186 (2013).

- Ko, H. et al. Ultrathin compound semiconductor on insulator layers for high-performance nanoscale transistors. *Nature* 468, 286–289 (2010).

- Ahn, J.-H. et al. Heterogeneous three-dimensional electronics by use of printed semiconductor nanomaterials. Science 314, 1754–1757 (2006).

- Wang, Y. et al. Field-effect transistors made from solution-grown twodimensional tellurene. Nat. Electron. 1, 228–236 (2018).

- Zhou, G. et al. High-mobility helical tellurium field-effect transistors enabled by transfer-free, low-temperature direct growth. Adv. Mater. 30, 1803109 (2018).

- Dutton, R. W. & Muller, R. S. Electrical properties of tellurium thin films. Proc. IEEE 59, 1511–1517 (1971).

- Okuyama, K. & Kumagai, Y. Grain growth of evaporated Te films on a heated and cooled substrate. J. Appl. Phys. 46, 1473–1477 (1975).

- 25. Weimer, P. A p-type tellurium thin-film transistor. *Proc. IEEE* **52**, 608–609 (1964).

- Okuyama, K., Yamamoto, H. & Kumagai, Y. Effect of Au nucleation centers and deposition rate on crystallinity and electronic properties of evaporated Te films. J. Appl. Phys. 46, 105–111 (1975).

- Dutton, R. & Muller, R. Large grain tellurium thin films. Thin Solid Films 11, 229–236 (1972).

- Wu, W., Qiu, G., Wang, Y., Wang, R. & Ye, P. Tellurene: its physical properties, scalable nanomanufacturing, and device applications. *Chem. Soc. Rev.* 47, 7203–7212 (2018).

- Chen, J. et al. Ultrathin β-tellurium layers grown on highly oriented pyrolytic graphite by molecular-beam epitaxy. Nanoscale 9, 15945–15948 (2017).

- Ellmer, K. & Mientus, R. Carrier transport in polycrystalline ITO and ZnO: Al II: the influence of grain barriers and boundaries. *Thin Solid Films* 516, 5829–5835 (2008).

- Dimitriadis, C. A., Coxon, P. A., Dozsa, L., Papadimitriou, L. & Economou, N. Performance of thin-film transistors on polysilicon films grown by low-pressure chemical vapor deposition at various pressures. *IEEE Trans. Electron Devices* 39, 598–606 (1992).

- 32. Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. *Science* **349**, aab2750 (2015).

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© The Author(s), under exclusive licence to Springer Nature Limited 2019

NATURE NANOTECHNOLOGY ARTICLES

#### Methods

**Thermal evaporation of Te thin films.** Te thin films were deposited in an Edwards Coating System (E306A thermal evaporator system) with a base pressure of about  $1.5\times10^{-6}$  mbar. Te pellets (99.999%, Sigma-Aldrich) were used as the thermal evaporation source. When the pressure reached  $2\times10^{-6}$  mbar, the substrate temperature was reduced to  $-80\,^{\circ}\text{C}$  by cooled nitrogen gas flow before the evaporation. The evaporation rate was controlled to be around  $10\,\text{Å}\,\text{s}^{-1}$  for all the evaporations. The thickness of Te thin film was monitored by during deposition. Following evaporation, the samples were taken out after the substrate temperature recovered to room temperature. All the Te thin films studied were prepared under these conditions, except for Te thin films evaporated at different substrate temperatures.

**Device fabrication.** *Single transistors.* FETs were fabricated on various substrates by the following photolithography, deposition and lift-off processes. First, gate regions were patterned on the SiO<sub>2</sub>/Si, PET, Kapton or quartz substrates and Ti/Au (2 nm/18 nm) gate electrodes were deposited by electron-beam evaporation. The ZrO<sub>2</sub> dielectric layer was then deposited by atomic layer deposition (ALD). For single transistors on SiO<sub>2</sub>/Si substrates, ZrO<sub>2</sub> was deposited at 200°C with a thickness of 5 nm. For transistors on PET and quartz, ZrO<sub>2</sub> was deposited at 110°C with a thickness of 10 nm. For transistors on Kapton, ZrO<sub>2</sub> was deposited at 110°C with a thickness of 20 nm. Following the gate fabrication, Te channel regions were patterned over the gate area and Te was deposited. After the lift-off process, source and drain regions were patterned. Ni (30 nm) was deposited by electron-beam evaporation as metal contact. For Te FETs on quartz, sputtered indium tin oxide was used as gate (20 nm) and contact material (25 nm) to enable device transparency.

Logic gates and circuits. For the logic circuits a  $10\,\mathrm{nm}~\mathrm{ZrO_2}$  layer was deposited at 200 °C by ALD as the dielectric layer. Via regions were etched by buffered hydrofluoric acid (HF) solution. Additionally, Ni/Au (20 nm/10 nm) contacts were used to avoid Ni etching by buffered HF solution.

Two-layered transistors and 3D inverters. The bottom layers were fabricated using the process described above. After the fabrication of the bottom layer, 30 nm  ${\rm SiO}_x$  was deposited on the top as an intermediate insulation layer by electron-beam evaporation and then the next layer was built on the top using the same procedure used for the first layer. ZrO $_2$  (10 nm) was deposited at 110 °C by ALD.

Characterizations. Te thin films with varying thickness were deposited on quartz substrates for the optical measurements. The thicknesses of Te thin films for optical bandgap measurements and thickness-dependent device performance were measured by atomic force microscope (AFM) (Dimension ICON AFM microscope (Bruker), operating in tapping mode). All other thickness measurements were based on the crystal quartz monitor. TEM characterization was performed on 9-nm-thick Te deposited on SiO2 support TEM membrane (TED PELLA). The Te film in Fig. 1c was patterned and transferred on a SiO2 support TEM membrane. TEM characterization was carried on an FEI Titan 60–300 microscope with an acceleration voltage of 200 kV at the National Center for Electron Microscopy at Lawrence Berkeley National Laboratory. The sample for XRD measurement was deposited on glass with a thickness of 50 nm (based on the quartz crystal monitor). XRD measurement was performed on an AXS D8 Discover GADDS, Bruker with a Co K $\alpha$ X-ray source (wavelength  $\lambda$  = 1.7903 Å). A Shimadzu SolidSpec-3700 spectrometer was used to measure the transmission and diffuse reflection of the

samples. The polarized light optical microscopy images of Te thin films were taken by a polarized LV100N optical microscope (Nikon). Room-temperature electrical measurements were performed in a probe station using a 4155C Semiconductor Parameter Analyzer (Agilent Technologies). Temperature-dependent electrical measurements were performed in a cryogenic probe station (LakeShore) with a B1500a Semiconductor Device Analyzer (Keysight). Effective mobility was calculated using

$$\mu_{\rm eff} = \frac{\mathrm{dI_d}}{\mathrm{d}V_\mathrm{d}} \frac{L}{WC_\mathrm{ox}(V_\mathrm{g} - V_\mathrm{t})} \tag{1}$$

where  $C_{\rm ox}$  is the gate oxide capacitance, L is the channel length, W is the device width and  $V_{\rm t}$  is the threshold voltage.  $I_{\rm d}$  was measured at low bias ( $V_{\rm d}$  = -0.1 V). Subthreshold swing (SS) is derived from the equation

$$SS = \left(\frac{d(\log I_{\rm d})}{dV_{\rm g}}\right)^{-1} \tag{2}$$

at the low bias ( $V_d = -0.1 \text{ V}$ ).

#### Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author on reasonable request.

#### **Acknowledgements**

Synthesis work was supported by the US Department of Energy, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division under contract No. DE-AC02-05CH11231 within the Electronic Materials Program (No. KC1201). Work at the Molecular Foundry was supported by the Office of Science, Office of Basic Energy Sciences, of the US Department of Energy under Contract no. DE-AC02-05CH11231. We thank N. Tamura for help with XRD measurements.

#### **Author contributions**

C.Z., C.T. and A.J. conceived the idea for the project. C.Z. and A.J. designed the experiments. C.Z., M.A. and Z.Y. fabricated the devices. C.Z. performed the device measurements. C.Z., C.T., X.S., D.-H.L., M.H., H.Y.Y.N., L.L. and M.S. performed material characterizations. C.Z. and A.J analysed the data. C.Z., C.T., D.-H.L. and A.J. wrote the manuscript. All authors discussed the results and commented on the manuscript.

#### **Competing interests**

The authors declare no competing interests.

#### **Additional information**

**Supplementary information** is available for this paper at https://doi.org/10.1038/s41565-019-0585-9.

Correspondence and requests for materials should be addressed to A.J.

Peer review information Nature Nanotechnology thanks Takhee Lee, SungWoo Nam and the other, anonymous, reviewer(s) for their contribution to the peer review of this work

Reprints and permissions information is available at www.nature.com/reprints.

### SUPPLEMENTARY INFORMATION

https://doi.org/10.1038/s41565-019-0585-9

In the format provided by the authors and unedited.

## Evaporated tellurium thin films for p-type fieldeffect transistors and circuits

Chunsong Zhao<sup>1,2,3,5</sup>, Chaoliang Tan<sup>1,2,5</sup>, Der-Hsien Lien<sup>1,2</sup>, Xiaohui Song<sup>3,4</sup>, Matin Amani<sup>1,2</sup>, Mark Hettick<sup>1,2</sup>, Hnin Yin Yin Nyein<sup>1,2,3</sup>, Zhen Yuan<sup>1,2</sup>, Lu Li<sup>1,2</sup>, Mary C. Scott<sup>3,4</sup> and Ali Javey<sup>1,2,4</sup>

<sup>&</sup>lt;sup>1</sup>Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA, USA. <sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA, USA. <sup>3</sup>Department of Materials Science and Engineering, University of California at Berkeley, Berkeley, CA, USA. <sup>4</sup>The Molecular Foundry, Lawrence Berkeley National Laboratory, Berkeley, CA, USA. <sup>5</sup>These authors contributed equally: Chunsong Zhao, Chaoliang Tan. <sup>\*</sup>e-mail: ajavey@eecs.berkeley.edu

### Supplementary Information

# Evaporated tellurium thin films for *p*-type field-effect transistors and circuits

Chunsong Zhao <sup>1,2,3,#</sup>, Chaoliang Tan <sup>1,2,#</sup>, Der-Hsien Lien<sup>1,2</sup>, Xiaohui Song<sup>3,4</sup>, Matin Amani<sup>1,2</sup>, Mark Hettick<sup>1,2</sup>, Hnin Yin Nyein<sup>1,2,3</sup>, Zhen Yuan<sup>1,2</sup>, Lu Li<sup>1,2</sup>, Mary C. Scott<sup>3,4</sup> and Ali Javey<sup>1,2,\*</sup>

<sup>1</sup>Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720, United States

<sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720, United States

<sup>3</sup>Department of Materials Science and Engineering, University of California at Berkeley, Berkeley, CA 94720, United States

<sup>4</sup>The Molecular Foundry, Lawrence Berkeley National Laboratory, Berkeley, CA, 94720, United States

\*These authors contribute equally to this work.

<sup>\*</sup>Address correspondence to <u>ajavey@eecs.berkeley.edu</u>

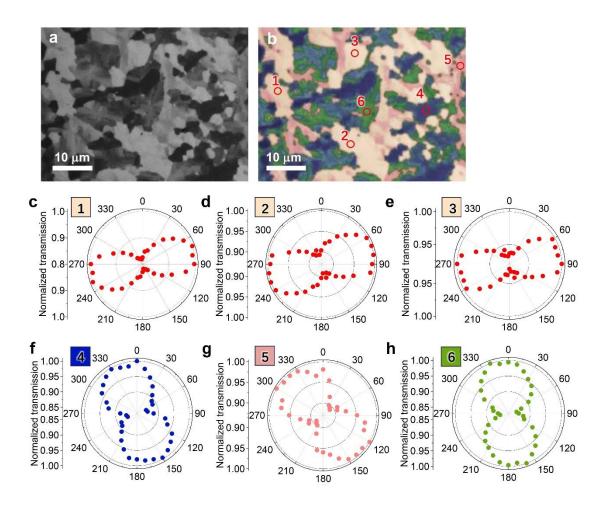

Supplementary Fig. 1. Polarized light microscopy images and polarized transmission measurements of different domains. a, The polarized light microscopy image of 9 nm Te film on quartz evaporated with a substrate temperature of -80 °C. b, The corresponding false-color polarized light microscopy image of a. c-e, The polar plots of normalized polarization-resolved transmission intensity at 550 nm from the labelled domains in b. f-h, The polar plots of normalized polarization-resolved transmission intensity at 550 nm from domains with the corresponding color in b.

Note: Supplementary Fig. 1a shows a polarized light microscopy image of 9 nm Te film with a smooth surface on quartz evaporated with a substrate temperature of -80 °C. Supplementary Fig. 1b shows the corresponding false-color polarized light microscopy image in a, in which the domains labeled with different colors. Supplementary Fig. 1c-e show polar plots of normalized polarization-resolved transmission intensity at 550 nm from domains with the same color in b, which clearly presents that they have almost the same orientation. Supplementary Fig. 1f-h show the polar plots of polarization-resolved transmission intensity at 550 nm from domains with the corresponding colors in b, which clearly presents that the domains with different colors have the different crystal orientations. The polarization-resolved transmission analysis can support that the contrast differences observed in polarized light microscopy images come from the gains with different crystal orientations.

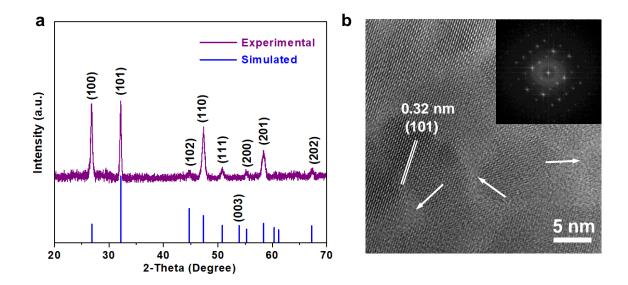

**Supplementary Fig. 2.** XRD and HRTEM results of evaporated Te films. a, XRD pattern of a Te thin film (50 nm) on quartz evaporated with a substrate temperature of -80 °C. b, HRTEM image of a Te thin film (9 nm) evaporated with a substrate temperature of -80 °C. Inset is the corresponding Fourier transform. The measured lattice distance is 0.32 nm, corresponding to the (101) planes of Te crystal.

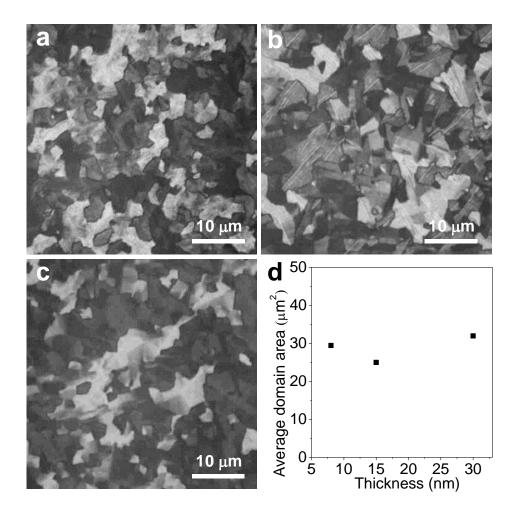

Supplementary Fig. 3. Polarized light microscopy images of Te films evaporated with a substrate temperature of -80 °C with different thicknesses. a, 8 nm; b, 15 nm; c, 30 nm. d, The calculated average domain areas of Te films with different thicknesses evaporated with a substrate temperature of -80 °C.

**Supplementary Fig. 4. Thickness-dependent optical properties of Te thin films evaporated with a substrate temperature of -80** °C. **a-c**, Reflection (**a**), transmission (**b**) and absorption (calculated as 100%-R-T) (**c**) of the evaporated Te films with varying thickness. **d**, Thickness-dependent absorption coefficient of evaporated Te films calculated from the data shown in panel **c**. The thicknesses are measured by AFM.

**Supplementary Fig. 5. Domain areas analysis of Te thin films evaporated with different substrate temperatures.** Polarized light microscopy images of Te films (9 nm) evaporated with different substrate temperatures: **a**, -60 °C; **b**, -35 °C; **c**, -10 °C; **d**, 25 °C. **e**, STEM image of Te film (9 nm) evaporated on a 25 °C substrate. **f**, The calculated average domain areas of Te films (9 nm) evaporated with different substrate temperatures.

Supplementary Fig. 6. Electrical characterization of Te field effect transistors.

**a**, The energy band diagram of the Te FET using Ni contacts. **b**, Room temperature effective mobility and on/off current ratio of Te FET (8 nm) evaporated with different substrate temperatures (the channel length = 8  $\mu$ m; the channel width = 8  $\mu$ m). **c-d**, Semi-logarithmic (**c**) and linear (**d**) scale plot of  $I_d$ - $V_g$  transfer curves of

the Te transistor (8 nm) in Fig. 2b under forward and reverse sweeping directions. **e**-**f**, Semi-logarithmic (**e**) and linear (**f**) scale plot of temperature-dependent  $I_d$ - $V_g$ transfer curves of Te FET (8 nm) measured over a range of 78 K to 300 K (the channel length = 8  $\mu$ m; the channel width = 8  $\mu$ m). **g**, Temperature-dependent effective mobility derived from the transfer curves in **e** (derivation details for effective mobility are introduced in Characterization section).

Supplementary Fig. 7. Flexible and transparent field effect transistors based on Te thin films evaporated with a substrate temperature of -80 °C. Optical image (a),  $I_d$ - $V_g$  (b) and  $I_d$ - $V_d$  (c) of a Te FET on PET (the channel length = 6  $\mu$ m; the channel width = 7  $\mu$ m). Optical image (d),  $I_d$ - $V_g$  (e) and  $I_d$ - $V_d$  (f) of a Te FET on quartz (the channel length = 9  $\mu$ m; the channel width = 8  $\mu$ m).

Supplementary Fig. 8. Effective mobility and on/off current ratio of Te FET (8 nm) on Kapton substrate under different strain conditions.

**FET based ICs. a-b**, Schematic diagram of an inverter (a) and NAND gates (b). c-d, Schematic diagram (c) and truth table (d) for Te FET based full-adder. The voltages indicated correspond to the outputs recorded from the device. e-f, Schematic diagram (e) and truth table (f) for Te FET based 2-bit multiplier. Voltages indicated correspond to the outputs recorded from the device.

Supplementary Fig. 10. Transfer curves for 2-layered transistors. a,  $I_d$ - $V_g$  curves measured on the 1<sup>st</sup> layer Te FET before and after fabrication of the 2<sup>nd</sup> layer. b, Effective mobility of the 1<sup>st</sup> layer Te FET before and after 2<sup>nd</sup> layer fabrication and 2<sup>nd</sup> layer Te FET derived at  $V_d$ =-0.1 V (first layer: the channel length = 6  $\mu$ m; the channel width = 8  $\mu$ m; second layer: the channel length = 5  $\mu$ m; the channel width = 8  $\mu$ m).