View Article Online

Cite this: Nanoscale, 2016, 8, 19876

# Fully gravure printed complementary carbon nanotube TFTs for a clock signal generator using an epoxy-imine based cross-linker as an n-dopant and encapsulant†

Donghwan Kim,<sup>a</sup> Younsu Jung,<sup>a</sup> Junfeng Sun,<sup>a</sup> Chisun Yeom,<sup>a</sup> Hyejin Park,<sup>a</sup> Dae Gon Jung,<sup>a</sup> Yeonkyeong Ju,<sup>a</sup> Kevin Chen,<sup>b</sup> Ali Javey<sup>b</sup> and Gyoujin Cho<sup>a</sup>

Printed p-type single walled carbon nanotube (SWCNT) based circuits exhibit high power dissipation owing to their thick printed dielectric layers (>2  $\mu$ m) and long channels (>100  $\mu$ m). In order to reduce the static power dissipation of printed SWCNT-base circuits while maintaining the same printing conditions and channel lengths, complementary metal-oxide-semiconductor (CMOS) based circuits are more ideal. These circuits, however, have not been successfully implemented in a scalable printing platform due to unstable threshold voltages of n-doped SWCNT based thin film transistors (TFTs). In this work, a thermally curable epoxy-imine-based n-doping ink is presented for achieving uniform doping and sealing of SWCNT layers by gravure printing. After printing the n-doping ink, the ink is cured to initiate a cross-linking reaction to seal the n-doped SWCNT-TFTs so that the threshold voltage of the n-doped SWCNT-TFTs is stabilized. Flexible CMOS ring oscillators using such n-doped SWCNT-TFTs combined with the intrinsically p-type SWCNT-TFTs can generate a 0.2 Hz clock signal with significantly lower power consumption compared to similarly printed p-type only TFT based ring oscillators. Moving forward, this CMOS flexible ring oscillator can be practically used to develop fully printed inexpensive wireless sensor tags.

Received 3rd October 2016, Accepted 11th November 2016 DOI: 10.1039/c6nr07762e

www.rsc.org/nanoscale

## Introduction

The popularity of printed electronics has drawn many efforts in developing printing systems where printers, materials and device designs are well matched to meet the demand for inexpensive, disposable, and flexible devices. Among these devices, the printed wireless cyclic voltammetry (CV) tag¹ has been considered as a prototype for realizing printed thin film transistor (TFT) integrated commercial products, integrating sensors, signage, amplifiers, logic circuits, and a power source all on one single relatively large area device at a low operating frequency. Furthermore, the required level of registration accuracy and pattern resolution to integrate TFTs in the wireless CV tag can be achievable on plastic or paper foils using gravure, flexographic, or offset printing.<sup>2,3</sup> In order to expedite the practical usage of such fully printed devices, a less-power-

Previously, p-type single-walled carbon nanotube (SWCNT) based TFTs (SWCNT-TFTs) have been utilized to develop a ring oscillator with operation frequencies ranging between 0.1 Hz to greater than 1 GHz in the wide range of operation power.<sup>7-9</sup> Such large differences in the operation frequency and voltage are dependent on the quality of the deposited SWCNT networks as well as the quality and dimensions of the deposited electrodes and dielectric layers for the construction of TFTs on rigid or flexible substrates.10 For devices fabricated on smooth, rigid substrates such as Si/SiO2, excellent percolating networks of SWCNTs can be obtained. In addition, a wide range of electrode and dielectric layer materials that can be deposited using vacuum processes allows for better ohmic contacts and high quality interfaces with the SWCNTs, enabling higher operation frequencies (>1 MHz). On the other hand, the rougher surfaces of printed substrates such as polyethylene terephthalate (PET) typically result in lower quality SWCNT networks. In particular, to enable direct gravure printing of SWCNTs, a polymer matrix is typically required to increase the

E-mail: ajavey@berkeley.edu

consuming printed ring oscillator for generating low frequency clock signals (<1 Hz) is necessary  $^{4-6}$  and should be fully printed through a scalable printing system such as gravure on flexible foils.

<sup>&</sup>lt;sup>a</sup>Sunchon National University, Printed Electronics Engineering in BK 21 Program, Sunchon, 540-742, Korea. E-mail: gcho@sunchon.ac.kr

<sup>&</sup>lt;sup>b</sup>University of California, Berkeley, California 94720, USA.

<sup>†</sup>Electronic supplementary information (ESI) available: Experimental details, photos, SEM, and comparative tables. See DOI: 10.1039/c6nr07762e

viscosity of the inks for compatibility with gravure printing, which also leads to significantly lower device performances. In addition, a limited range of metal and dielectric inks makes it difficult to create ohmic contacts to SWCNTs. Unlike vacuum based processes such as atomic layer deposition (ALD), printed dielectric layers also cannot be easily controlled down to angstrom level roughnesses and generally contain mobile or fixed charges at the interfaces, leading to reduced performance.11 All of these factors, in addition to larger source/drain to gate overlap capacitances due to alignment tolerances, lead to lower device performance and lower operating frequencies.

However, even with these limitations, printed SWCNT-TFTs have shown to be a promising candidate for large area electronics and disposable devices where performance requirements may not be as high as in traditional electronics systems. The high throughput of gravure printing allows for the mass production of electronics at a very low cost per area, making it an ideal platform for achieving these goals.

Currently, most of the printed SWCNT-TFT circuits have been based upon PMOS only architectures, which have much higher static power dissipation compared to CMOS. In order to reduce the power dissipation of printed SWCNT-based ring oscillators while maintaining the same printing system and device structure, CMOS SWCNT-based ring oscillators, 12,13 printed by a scalable printing method, are strongly demanded. However, fully printed CMOS circuits have not yet been demonstrated as most printing compatible n-type doping schemes such as poly(ethylene imine) (PEI), 14 poly(ethylene oxide),15 or piperidine16 typically exhibiting large threshold voltage variations.

Here, we demonstrate a thermally curable epoxy-iminebased ink for n-type doping of printed SWCNTs as well as encapsulating the SWCNT layers from the surroundings by one simple printing process. Fully gravure-printed CMOS ring oscillators printed utilizing this doping scheme can successfully generate a stable clock signal at an operating voltage of 5 V with lower power dissipation compared to PMOS only printed signal generators. Such fully printed CMOS ring oscillators can be used in developing CMOS printed digital circuits, particularly for constructing inexpensive and disposable wireless sensor tags<sup>1,17,18</sup> where less than 50 TFTs are integrated and the operation frequency is less than 1 Hz. 19,20

# **Experimental section**

#### **Materials**

A 100 µm thick poly(ethyleneterephtalate) (PET) film with 200 mm width was purchased from SKC, Korea and used without further surface treatment. Silver nanoparticle based ink (PG-007 BB) was obtained from Paru Co. Korea and formulated by adding dipropylene glycol methyl ether (Aldrich) to obtain the appropriate viscosity (500 cp) and surface tension (47 mN m<sup>-1</sup>) for printing the gate and drain-source electrodes using roll-to-plate gravure. BaTiO3 nanoparticle based ink (PD-100, Paru Co., Korea) was purchased from Paru Co. Korea

and further formulated to obtain a viscosity of 73 cp and a surface tension of 32 mN m<sup>-1</sup> using ethyl 2-cyanoacrylate (Aldrich) for printing the dielectric layers. For printing the channel, single walled carbon nanotube (SWCNT) based ink (PR-040, Paru Co., Korea) was obtained and diluted by using diethylene glycol monobutyl ether (Daejung Co., Korea). For n-doping and encapsulation, SU-8 (Microchem) was formulated using diethylene glycol (Aldrich).

#### **Printing process**

A roll-to plate (R2P) gravure printer (Fig. 1a) manufactured by i-PEN, Korea was used in the printing of the SWCNT-TFTs. For printing the gate electrodes, the roll pressure of the R2P gravure was maintained at 5 kgf cm<sup>-2</sup> with a printing speed of 18 m min<sup>-1</sup>. The printed gate electrode layer was annealed for 1 min at 150 °C and then, the dielectric layer was printed using a printing speed of 20 m min<sup>-1</sup> and a roll pressure of 7.5 kgf cm<sup>-2</sup>. The printed dielectric layer was also annealed for 1 min at 150 °C. SWCNT layers were printed with a printing speed of 30 m min<sup>-1</sup> and a roll pressure of 4 kgf cm<sup>-2</sup> and then annealed for 1 min at 150 °C. The drain-source electrodes were printed with a speed of 20 m min<sup>-1</sup> and a roll pressure of 5 kgf cm<sup>-2</sup> and then annealed for 1 min at 150 °C as well. Finally, n-doping was carried out using a blade coating method with the formulated SU-8 based ink, and the resulting n-doped ink was cross-linked by thermal treatment for 1 min at 150 °C. This heat treatment also encapsulates the n-doped channel to provide device stability by preventing exposure of the SWCNT layers to the surrounding environment.

#### Measurements

All inks were characterized using a DCAT21 (Dataphysics Co., Germany) and SV-10 Vibro viscometer for measuring the surface tension and viscosity of the inks, respectively. All measurements in this work were carried out under ambient conditions. The printed SWCNT-TFTs were characterized using a semiconductor parameter analyzer (4155C, Agilent, USA) and a digital phosphor oscilloscope (DPD 4054, Tektronix, USA) was used to characterize the fully printed inverters and ring oscillators.

## Results and discussion

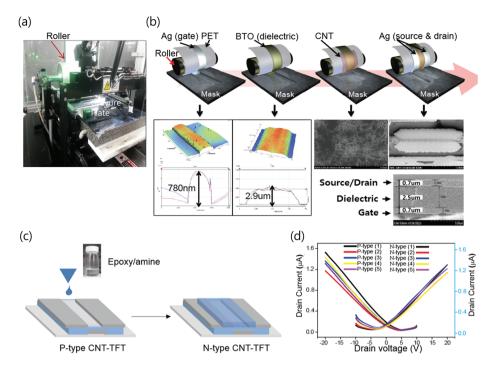

In this work, roll-to-plate (R2P) gravure (Fig. 1a) has been used to fully print the gate, dielectric, active, and drain-source layers to integrate ten SWCNT-TFTs into a five stage CMOS ring oscillator. A back-gated TFT device architecture with a channel length of 150 µm and a width of 4000 µm is explored so that the active SWCNT channel is accessible for doping.

For the printing of the TFTs, the gate electrodes are first printed onto PET foil using a silver nanoparticle based ink (PG-007, Paru, Korea). The electrodes were measured to have an average thickness of  $700 \pm 50$  nm with a surface roughness of approximately 64 ± 10 nm (Fig. 1b) and a sheet resistance of  $3 \pm 0.1 \text{ m}\Omega \text{ sq}^{-1} \text{ mil}^{-1}$ . A BaTiO<sub>3</sub> nanoparticle based dielectric

**Paper** Nanoscale

Fig. 1 Printing process of a printed CMOS circuit. (a) Image of the R2P gravure printer used in this work and (b) a schematic view of the R2P gravure printing process for printing the gate, dielectric, active and drain-source layers along with their respective 3D images, cross-sectional profiles, and SEM image. (c) Descriptive illustration of the n-doping process and (d)  $I_d - V_g$  characteristics before and after the n-type doping of the SWCNT-TFTs.

ink (PD-100, Paru, Korea) is then printed onto the gate electrodes with a resulting thickness of 2.7  $\pm$  0.2  $\mu m$  and a surface roughness of 94 ± 10 nm (Fig. 1b). From the capacitancevoltage (C-V) measurements on metal/insulator/metal test structures, the printed dielectric layers show a capacitance of 7 nF cm<sup>-2</sup> (see Fig. S1a in the ESI†). A SWCNT-based ink (PR-040, Paru, Korea) is printed onto the dielectric layer as the active channel material. As the n-doping process slightly lowers the on-current of the TFTs, two different SWCNT loading concentrations are utilized to generate two different current levels (see Fig. S2 in the ESI†). For the NMOS portion of the ring oscillators, undiluted SWCNT ink is used to obtain the maximum on-current. For the PMOS portion, a diluted SWCNT ink is used to lower the on-current so as to match the n-doped NMOS TFTs. After printing on the SWCNT inks, the drain-source layers are printed using silver ink to complete the printing of the TFTs. C-V measurements of printed metal/ insulator semiconducting (MIS) SWCNT test structures show the characteristic capacitance behaviour of MIS devices  $(20.5 \text{ nF cm}^{-2} \text{ at } -20 \text{ V}, \text{ dropping down to } 7.3 \text{ nF cm}^{-2} \text{ at } 20 \text{ V})$ with small hysteresis (see Fig. S1b in the ESI†). No short circuiting is observed for the 10 TFTs.

The conversion from p-type to n-type SWCNT-TFTs is carried out by simple blade coating of an epoxy-imine-based n-doping ink, formulated using a commercially available epoxy based photoresist (SU-8 from Microchem) as shown in Fig. 1c. The converting mechanism from p-type to n-type SWCNT-TFTs will be the same as the previously reported one 14,21 where

SWCNT can be n-doped by replacing the absorbed oxygen with a nitrogen group of the polyethylene imine (PEI). We speculate that the nitrogen group in SU-8 will play the same role which can provide electrons from the unbound electron pairs of nitrogen. 14,21 The transfer characteristics of the ten p-type and n-type SWCNT-TFTs in a representative 5-stage ring oscillator are shown in Fig. 1d. The PMOS TFTs exhibit an average oncurrent of 1.36  $\pm$  0.13  $\mu$ A and an on/off ratio of 10<sup>3</sup> while the NMOS TFTs have an average on-current of 1.06 ± 0.13 µA with an on/off ratio of 10<sup>2</sup> (see Fig. S3 in the ESI†). The lower on/off ratios in the NMOS TFTs originate from the higher SWCNT loading, which leads to more percolation of metallic SWCNTs within the channel. The threshold voltages  $(V_{th})$  for the PMOS and NMOS SWCNT-TFTs range from 0 to 4 V and 0 to −2 V, respectively (see Fig. S2 and S3 in the ESI†).

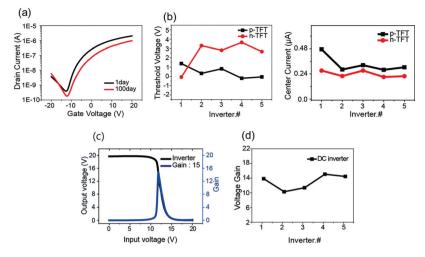

For almost all device applications using SWCNT-based circuits, air stability is crucial. Therefore, re-adsorption of oxygen or moisture which diffuses through the adsorbed PEI layers has been considered to be one major factor for the electrical variations and air stability in PEI doped n-type SWCNT-TFTs.<sup>22</sup> Due to the excellent passivation in our SU-8 based n-doping ink, our n-doped SWCNT-TFTs show high air stability for up to 3 months (Fig. 2a).

For proper operation of the ring oscillators, the variation in  $V_{\rm th}$  and on-currents (see Fig. S4 in the ESI†) in the SWCNT-TFT is critical. In order to understand the amount of variation that can be tolerated for this system p-spice simulations were conducted using experimentally extracted parameters from the

Fig. 2 Electronic performance of printed n-type and p-type SWCNT-TFTs (a) Stability of the printed n-type SWCNT-TFTs was proved by measuring the transfer characteristics of the converted n-type SWCNT-TFTs stored under an ambient atmosphere just after printing (black line) and after 100 days (red line). (b) Threshold voltage and on-currents of 5 n-type SWCNT-TFTs and 5 p-type SWCNT-TFTs within a 5-stage CMOS ring oscillator. (c) Voltage transfer curve of a CMOS inverter with high voltage gains at an input voltage of 20 V. (d) The voltage gains of 5 CMOS inverters within the ring oscillator.

printed n and p-type SWCNT-TFTs. From the simulations, a maximum of 30% variation in the on-currents can be tolerated before significant reductions in the clock speed occur (refer to the p-spice simulation results in Fig. S4 in the ESI†). These results show that the printed CMOS ring oscillators are more tolerant to on-current variations when compared with their PMOS only counterparts.

To reduce device-to-device variation, any parameter of the printing system that influences the parasitic capacitances in the SWCNT-TFTs has to be well controlled. For printed electronics, the inaccuracy of the drain-source electrode alignment with respect to the printed gate electrodes has been known as a major factor that must be better controlled.<sup>23</sup> In our system, an overlay printing registration accuracy of  $\pm 10 \, \mu m$  is achieved. In addition, by maintaining a constant rheology among the employed inks (silver ink, BaTiO3 ink, SWCNT ink, and n-doping ink) and optimizing printing conditions (printing

speed, impression roller pressure, and blade angle) the surface roughness of the printed dielectric layers, evenness of the printed SWCNT network density, thickness of the printed dielectric layers, and the edge roughness of the printed drainsource electrodes are all maintained to be stochastically constant with less than 10% variation across different

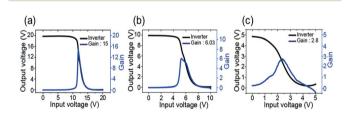

Fig. 4 Voltage transfer curves of a CMOS inverter at input voltages of (a) 20 V, (b) 10 V, and (c) 5 V.

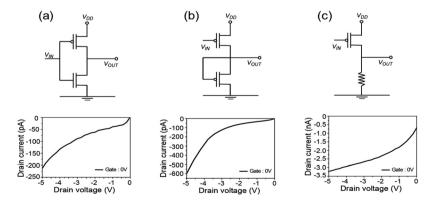

Fig. 3 Circuit schematics and ID-VD curves for the (a) CMOS, (b) PMOS-only, and (c) resistive load inverters to compare their respective static power consumptions.

**Paper**

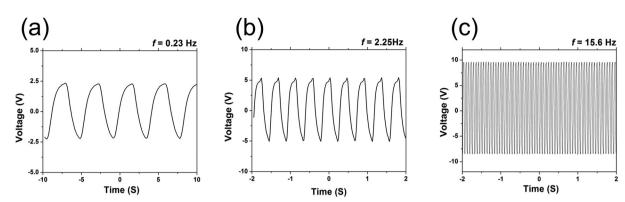

Fig. 5 Output characteristics of a five-stage CMOS ring oscillator (a) displaying output frequencies of 0.2 Hz at 5 V, (b) 2.3 Hz at 11 V, and (c) 15.6 Hz at 18 V.

devices.  $^{24}$  The  $V_{\rm th}$  and average on-currents of the gravure-printed n-type and p-type SWCNT-TFTs are listed in Fig. 2b. Although one out of the 10 SWCNT-TFTs do not fall within a 30% variation range, good switching behaviour and clock signal generation can still be obtained as shown later. Fig. 2c shows the voltage transfer curve of a representative CMOS inverter, with a gain of 15 V/V at an operating voltage of 20 V and Fig. 2d shows the gains of all 5 inverters within the 5-stage ring oscillator.

One important advantage of CMOS inverter designs is that there is lower static power dissipation. To prove this, we printed and measured 3-different types of SWCNT-TFT based inverters including CMOS, PMOS-only and PMOS with a resistive load to compare their relative static power consumptions (Fig. 3). The static power consumptions for each of the inverters at  $V_{\rm ds} = -5$  V were respectively estimated to be 1.06 nW, 2.99 nW and 16.1 nW for the CMOS, PMOS-only, and resistively loaded PMOS architectures. As such, the implementation of CMOS ring oscillators can potentially reduce the power consumption of printed SWCNT-TFT based electronic devices by 3 to 15 times over traditional PMOS only designs.

In addition to lower current draw, lower operating voltages are also important to achieve lower power consumption. The input voltage dependent voltage gains of the CMOS inverters ranging from 20 to 5 V are shown in Fig. 4. Based on the results of our previous fully printed RF 1-bit tone generating tags<sup>25</sup> and full adders, <sup>26</sup> a voltage gain of 3 is sufficient for operating simple TFT circuits (less than 50 TFTs) with a reasonable degree of functionality. Based on this requirement, the fully gravure-printed CMOS inverters demonstrated in this work can be operated at as low as 5 V. As shown in Fig. 5a, a 0.2 Hz clock signal can be successfully generated from our fully printed 5 stage CMOS ring oscillator with a 5 V input (Fig. 5a), while 2.3 Hz and 15.6 Hz clock signals can be generated with 10 V and 20 V inputs, respectively (Fig. 5b and c). Although the performance of our gravure-printed CMOS ring oscillators is lower than SWCNT-based CMOS ring oscillators fabricated using vacuum processes, 27,28 the attained clock signals at relatively low operating voltages is a good starting

point for further development in the field of printed wireless CV tags.

## Conclusions

In summary, for the first time, a CMOS ring oscillator has been realized with a fully printed, scalable gravure printing method using three different nanomaterial (silver nanoparticles, BaTiO<sub>3</sub> nanoparticles, and SWCNTs) based inks and a convenient n-doping ink through R2P gravure printing on PET foils. The n-doping ink based upon an epoxy-imine based resin has been specifically designed to convert p-type SWCNT-TFTs to n-type SWCNT-TFTs by simply printing onto a p-type SWCNT channel. The epoxy-imine-based n-doping ink has been designed to encapsulate the SWCNTs from being exposed to the surroundings after curing to provide air stability. Utilizing this doping scheme, SWCNT-TFT based CMOS flexible ring oscillators capable of generating a 0.2 Hz clock signal at DC 5 V can be realized. This operation voltage can be further decreased (~1.5 V) by employing the pure semiconducting SWCNTs<sup>29</sup> or monochiral SWCNTs.<sup>30</sup> Consequently, this R2P gravure system including the inks and circuit design to print a CMOS-type flexible ring oscillator can be practically used to develop a new field of fully printed wireless CV tags.

# Acknowledgements

This research was supported by a grant (16163MFDS001) from the Ministry of Food and Drug Safety in 2016 and RIC at Sunchon National University. A. J. acknowledges support from the NSF NASCENT Center.

### Notes and references

1 Y. Jung, H. Park, J. Noh, M. Jung, M. Pyo, K. Chen, A. Javey and G. Cho, *Sci. Rep.*, 2015, 5, 8105.

- 2 H. Yan, Z. Chen, Y. Zheng, C. Newman, J. Quinn, F. Dötz, M. Kastler and A. Facchetti, Nature, 2009, 457, 679-689.

- 3 Y. Yang, J. Park, I. You, S. Hong, H. Yun, Y. Kang, C. Lee and S. Cho, J. Ceram. Process. Res., 2015, 16, 276-279.

- 4 E. Cantatore, T. Geuns, G. Gelinck, E. Veenendaal, A. Gruijthuijsen, L. Schrijnemakers, S. Drews D. Leeuw, IEEE. J. Solid-State Circuits, 2007, 42, 84-92.

- 5 H. Kempa, M. Hambsch, K. Reuter, M. Stanel, G. Schmidt, B. Meier and A. Hübler, IEEE Trans. Electron Devices, 2011, 58, 2765-2769.

- 6 U. Zschieschang, H. Klauk, M. Halik, G. Schmid and C. Dehm, Adv. Mater, 2003, 15, 1147-1151.

- 7 M. Jung, J. Kim, H. Koo, W. Lee, V. Subramanian and G. Cho, J. Nanosci. Nanotechnol., 2014, 14, 1303-1317.

- 8 A. Bachtold, P. Hadley, T. Nakanishi and C. Dekker, Science, 2001, 294, 1317-1320.

- 9 J. Noh, M. Jung, K. Jung, G. Lee, S. Lim, D. Kim, S. Kim, J. Tour and G. Cho, Org. Electron, 2011, 12, 2185-2191.

- 10 J. Noh, M. Jung, K. Jung, S. Lim, G. Lee, V. Subramanian, A. Leonard, J. Tour and G. Cho, J. Appl. Phys., 2010, 108, 102811.

- 11 M. L. Chabinyc, R. Lujan, F. Endicott, I. McCulloch and M. Heeney, Appl. Phys. Lett., 2007, 90, 233508.

- 12 J. Zhang, C. Wang, Y. Fu, Y. Che and C. Zhou, ACS Nano, 2011, 5, 3284-3292.

- 13 H. Wang, P. Wei, Y. Li, J. Han, H. Lee, B. Naab, N. Liu, C. Wang, E. Adijanto, B. Tee, S. Morishita, Q. Lim, Y. Gao, Y. Cui and Z. Bao, Proc. Natl. Acad. Sci. U. S. A., 2014, 111, 4776-4781.

- 14 M. Shim, A. Javey, N. Kam and H. Dai, J. Am. Chem. Soc., 2001, 123, 11512-11513.

- 15 G. Siddons, D. Merchin, J. Back, J. Jeong and M. Shim, Nano. Lett., 2004, 4, 927-931.

- 16 K. Raj, Q. Zhang, C. Liu and M. B. C. Park, Nanotechnol., 2011, 22, 245306.

- 17 T. C. Huang, K. Fukuda, C. M. Lo, Y. H. Yeh, T. Sekitani, T. Someya and K. T. Cheng, IEEE Trans. Electron Devices, 2011, 58, 141-150.

- 18 H. Klauk, U. Zschieschang, J. Pflaum and M. Halik, Nature, 2007, 445, 745-748.

- 19 T. Sekitani, U. Zschieschang, H. Klauk and T. Someya, Nat. Mater., 2010, 9, 1015-1022.

- 20 H. Yan, Y. Zheng, R. Blache, C. Newman, S. Lu, J. Woerle and A. Facchetti, Adv. Mater., 2008, 20, 3393-3398.

- 21 Y. Nonoguchi, K. Ohashi, R. Kanazawa, K. Ashiba, K. Hata, T. Nakagawa, C. Adachi, T. Tanase and T. Kawai, Sci. Rep., 2013, 3, 3344, DOI: 10.1038/srep03344.

- 22 T. Yasunishi, S. Kishimoto and Y. Ohno, Jpn. J. Appl. Phys., 2014, 53, 05FD01.

- 23 H. Koo, W. Lee, Y. Choi, J. Sun, J. Bak, J. Noh, V. Subramanian, Y. Azuma, Y. Majima and G. Cho, Sci. Rep., 2015, 5, 14459.

- 24 W. Lee, H. Koo, J. Sun, J. Noh, K. Kwon, C. Yeom, Y. Choi, K. Chen, A. Javey and G. Cho, Sci. Rep., 2015, 5, 17707.

- 25 M. Jung, J. Kim, J. Noh, N. Lim, C. Lim, G. Lee, J. Kim, H. Kang, K. Jung, A. D. Leonard, J. M. Tour and G. Cho, IEEE Trans. Electron Devices, 2010, 57, 571-580.

- 26 J. Noh, K. Jung, J. Kim, S. Kim, S. Cho and G. Cho, IEEE Electron Device Lett., 2012, 33, 1574-1576.

- 27 M. Ha, Y. Xia, A. A. Green, W. Zhang, M. J. Renn, C. H. Kim, M. C. Hersam and C. Frisbie, ACS Nano, 2010, 4, 4388-4395.

- 28 Y. Awano, S. Sato, M. Hihei, T. Sakai, Y. Ohno and T. Mizutani, *Proc, IEEE.*, 2010, **98**, 2015–2031.

- 29 J. Ding, Z. Li, J. Lefebvre, F. Cheng, J. Dunford, R. Malenfant, J. Humes and J. Kroeger, Nanoscale., 2015, 7, 15741-15747.

- 30 M. Rother, S. Schieβl, Y. Zakharko, F. Gannott and J. Zaumseil, ACS Appl. Mater. Interfaces, 2016, 8, 5571-5579.