#

## Nanoscale InGaSb Heterostructure Membranes on Si Substrates for High Hole Mobility Transistors

Kuniharu Takei,  $^{\dagger,\pm,\$,\nabla}$  Morten Madsen,  $^{\dagger,\pm,\$,\nabla,\bigstar}$  Hui Fang,  $^{\dagger,\pm,\$}$  Rehan Kapadia,  $^{\dagger,\pm,\$}$  Steven Chuang,  $^{\dagger,\pm,\$}$  Ha Sul Kim,  $^{\dagger,\pm,\$}$  Chin-Hung Liu,  $^{\perp}$  E. Plis,  $^{\parallel}$  Junghyo Nah,  $^{\dagger,\pm,\$}$  Sanjay Krishna,  $^{\parallel}$  Yu-Lun Chueh,  $^{\perp}$  Jing Guo,  $^{\#}$  and Ali Javey\*,  $^{\dagger,\pm,\$}$

<sup>†</sup>Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, United States <sup>‡</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, United States <sup>§</sup>Berkeley Sensor and Actuator Center, University of California, Berkeley, California 94720, United States <sup>II</sup>Electrical and Computer Engineering, University of New Mexico, Albuquerque, New Mexico 87106, United States <sup>II</sup>Materials Science and Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan <sup>#</sup>Electrical and Computer Engineering, University of Florida, Gainesville, Florida 32611, United States

**Supporting Information**

**ABSTRACT:** As of yet, III–V p-type field-effect transistors (p-FETs) on Si have not been reported, due partly to materials and processing challenges, presenting an important bottleneck in the development of complementary III–V electronics. Here, we report the first high-mobility III–V p-FET on Si, enabled by the epitaxial layer transfer of InGaSb heterostructures with nanoscale thicknesses. Importantly, the use of ultrathin (thickness, ~2.5 nm) InAs cladding layers results in drastic performance enhancements arising from (i) surface passivation of the InGaSb channel, (ii) mobility enhancement due to the confinement of holes in InGaSb, and (iii) low-resistance, dopant-free contacts due to the type III band alignment of the heterojunction. The fabricated p-FETs display a peak effective

mobility of ~820 cm<sup>2</sup>/(V s) for holes with a subthreshold swing of ~130 mV/decade. The results present an important advance in the field of III–V electronics.

**KEYWORDS:** III–V-on-insulator, MOSFETs, XOI, two-dimensional membranes, heterojunction

**T** igh-mobility III–V compound semiconductors have been extensively explored as a potential replacement for the active channel material of scaled transistors with the promise of delivering high ON currents at low voltages.<sup>1-4</sup> Integration on Si substrates is required in order to present a scalable, costeffective platform. Conventionally, these materials are epitaxially grown on III-V wafers,<sup>1,2,4</sup> which have limited their use for consumer electronics due to the relatively high costs. In the past several years, direct growth of complex III-V multilayers has been demonstrated for enabling InGaAs-based n-FETs on Si substrates.<sup>5</sup> The large lattice mismatch of III–V semiconductors and Si, however, presents a challenge in the successful epitaxial growth of the layers with low defect densities.<sup>6,7</sup> This problem is especially prominent for Sb-based semiconductors,<sup>6</sup> such as  $In_xGa_{1-x}Sb$ , which are the most promising candidates for high hole mobility active layers.<sup>2,8–10</sup> For instance, InSb and GaSb have large lattice mismatches of  $\sim$ 19% and  $\sim$ 12% with Si, respectively.<sup>2</sup> Recently, epitaxial layer transfer (ELT)<sup>11-13</sup> of ultrathin InAs layers onto Si/SiO2 substrates<sup>14-16</sup> has been demonstrated for integrating n-type III-V semiconductors on Si

substrates. The approach is termed XOI, referring to the III-Von-insulator device architecture that resembles the conventional Si-on-insulator (SOI) substrates. In the XOI framework, the choice of the active semiconductor layer is decoupled from the support substrate.<sup>17</sup> High electron mobility ( $\mu_n = 4000-1000$  $cm^2/(V s)$ ) InAs XOI n-FETs with performances better than conventional Si MOSFETs of comparable length scales have been demonstrated.<sup>14</sup> A challenge, however, remains in the fabrication of high hole mobility III-V p-FETs and more specifically on Si substrates. Recently, buried channel, strained InGaSb p-FETs on III-V substrates have been reported with an effective hole mobility of  $\sim 1230 \text{ cm}^2/(\text{V s})$ , higher than that of Si or unstrained Ge p-MOSFETs.<sup>8,18</sup> These results are promising, clearly demonstrating the need for integration of a high hole mobility III-V semiconductor, such as InGaSb, on Si in order to realize III-V CMOS electronics. In this work,

```

Received:January 18, 2012Revised:March 1, 2012Published:March 12, 2012

```

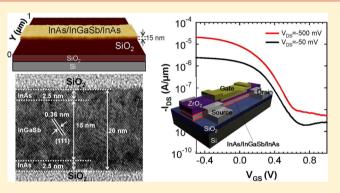

**Figure 1.** InAs/InGaSb/InAs heterostructure XOI. (a) Process schematic illustrating the fabrication of ultrathin InAs/InGaSb/InAs XOI substrates. The initial structure (1) is first prepatterned into NRs by lithography and wet etching (2). Afterward, the AlGaSb sacrificial layer is etched to partially release the NRs (3) which are subsequently transferred onto a Si/SiO<sub>2</sub> substrate by employing a PDMS slab (4). (b,c) AFM images of transferred InAs/InGaSb/InAs NRs on a Si/SiO<sub>2</sub> substrate with a width and height of ~350 and ~15 nm ( $T_{InGaSb}$  = 10 nm), respectively. (d) TEM image of an InAs/InGaSb/InAs XOI ( $T_{InGaSb}$  = 15 nm).

ELT of ultrathin  $InAs/In_{0.3}Ga_{0.7}Sb/InAs$  heterostructures is utilized for the fabrication of p-type XOI FETs on Si substrates. Here, InGaSb is used as the channel material with a ~2.5 nm thick InAs capping layer for passivation of the surface and for dopant-free, low-resistance contacts. Importantly, the use of this few layer thick interfacial InAs layer is essential for (i) fabrication of devices without significant InGaSb oxidation, (ii) hole confinement in the channel, and (iii) ohmic metal contact formation, without dopant profiling.

The process schematic for the fabrication of InAs/InGaSb/ InAs heterostructure XOI is depicted in Figure 1a. First,  $Al_{0.2}Ga_{0.8}Sb$  (thickness, 60 nm), InAs (thickness, 3 nm),  $In_{0.3}Ga_{0.7}Sb$  (thickness, 7–15 nm), and InAs (thickness, 3 nm) layers are epitaxially grown on a (100) GaSb wafer by molecular beam epitaxy (MBE). In this stack, AlGaSb is the sacrificial layer for the ELT technique, and InAs layers are the surface cladding caps for InGaSb channel material. InAs/ InGaSb/InAs layers were patterned into nanoribbon (NR) structures by lithography and wet etching (see Supporting Information). The NRs were subsequently picked and transferred onto a Si/SiO<sub>2</sub> receiver substrate by the use of a polydimethylsiloxane (PDMS) slab as previously demonstrated for the ELT of InAs.<sup>14</sup> Atomic force microscopy (AFM) images of the resulting NRs on a Si/SiO<sub>2</sub> substrate are shown in Figure 1b,c, clearly depicting that uniform layer transfer can be achieved with minimal surface roughness.

The high quality of the single crystalline InAs/InGaSb/InAs XOI layers is evident from transmission electron microscopy (TEM, Figure 1d). As shown, the InAs layers were slightly reduced in thickness (by ~0.5 nm) during the XOI transfer process, which is attributed to removal of a thin native oxide layer during the XOI processing steps. InAs cladding layers affect the energy band alignment of the system, as explained in detail below, while passivating the highly reactive InGaSb layer from oxidation during the ELT and subsequent device processing. For instance, the control samples prepared without the use of InAs cap resulted in the oxidation of the InGaSb layer by up to ~6 nm on each side (a loss of 12 nm total), as shown in Figure S1, Supporting Information.

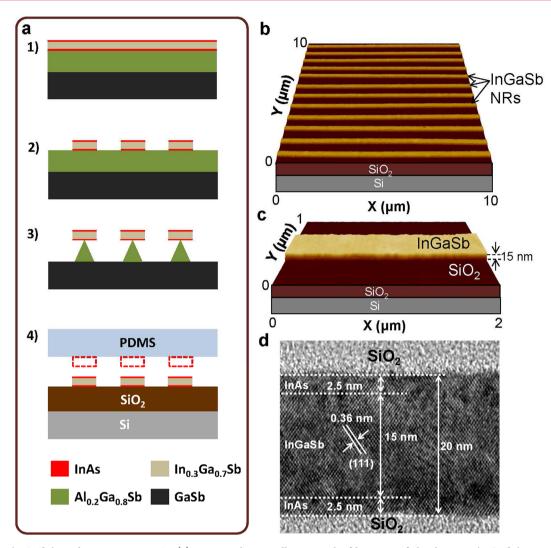

Device simulation (NextNano) was used to calculate the energy band diagram of the InAs/InGaSb/InAs XOI heterostructure (Figure 2). The device consists of two distinct regions.

**Figure 2.** Simulated energy band diagrams of InAs/InGaSb/InAs heterostructure XOI. Energy band diagrams under (a) the metal contact and (b) the channel region at the flat band condition. The conduction and valence band edges,  $E_c$  and  $E_v$ , and the ground state of electrons ( $e_1$ ) and heavy holes (hh<sub>1</sub>) are shown.

One is the region under the source/drain (S/D) metal (Ni) contacts where the conduction band of InAs is assumed to be ohmically contacted to the metal.<sup>19</sup> In this case, the electrons in the ultrathin InAs cap are not confined due to ohmic contact to the metal. Holes in InGaSb are partially confined. The InAs/ InGaSb interface under the metal contact was found to exhibit a broken gap (i.e., type III) band alignment for the explored InGaSb thickness range (7-15 nm) with the ground state of electrons in InAs being below the ground state of holes in InGaSb (Figure 2a). This "broken gap" band structure results in a semimetallic behavior, thereby, allowing for dopant-free contact to the valence band of InGaSb with relatively low resistances, as discussed later in this paper. The second energy band diagram corresponds to the channel region (Figure 2b). Here, InAs cap layers are in contact with large band gap dielectrics (ZrO<sub>2</sub> on the top and SiO<sub>2</sub> on the bottom surfaces) which effectively serve as potential barriers for electrons. As a result, the 2.5 nm InAs cap is highly confined. In this case, the InAs/InGaSb exhibits a staggered gap band alignment (i.e., type II), with the ground state of electrons in InAs being above that of the holes in InGaSb. As a result, in this case, the material stack behaves like a conventional quantum-well device, especially for holes which are highly confined in the InGaSb channel. This results in a 2-D hole gas, where the carriers are separated from the surface by the thickness of the InAs cap, likely reducing the severity of surface scattering at the InAs/high-K interface.

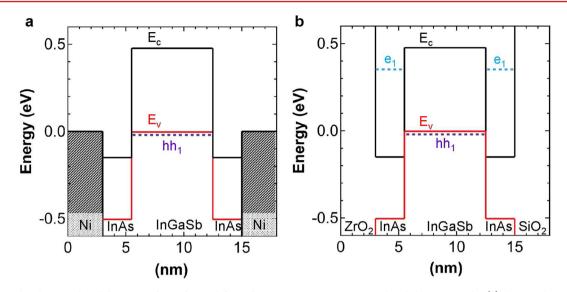

The electrical properties of InAs/InGaSb/InAs heterostructure XOI were probed by fabricating back- and top-gated devices. Back-gated p-FETs were fabricated by patterning Ni (thickness, 40 nm) source (S) and drain (D) contacts. The heavily doped Si substrate was used as the global back-gate with a 50 nm thermally grown SiO<sub>2</sub> as the back-gate dielectric. The devices were then capped with ~8 nm ZrO<sub>2</sub> by atomic layer deposition (ALD) in order to isolate them from the ambient environment (i.e., humidity and other contaminants). Specifically, ZrO<sub>2</sub> was chosen since it has been shown previously that ZrO<sub>2</sub>/InAs interface exhibits a low density of interface traps.<sup>14</sup> Figure 3a shows representative transfer characteristics of a backgated InAs/InGaSb/InAs XOI p-FET with an active channel thickness of  $T_{InGaSb}$  = 15 nm. Here, the device has a long channel length of  $L \sim 3 \ \mu m$  in order to study the carrier mobility, where diffusive transport is necessary. The effective hole mobility,  $\mu_p$ , of the device was then extracted as a function of the vertical field (i.e., gate voltage) by using  $\mu_p = g_D \times (L/W)$

× (1/(

$$C_{\rm g}(V_{\rm GS} - V_{\rm th})$$

)), where  $g_{\rm D} = \frac{dI_{\rm DS}}{dV_{\rm DS}}\Big|_{V_{\rm GS}}$ ,  $C_{\rm g}$  is the total

gate capacitance in the ON state, W is the channel width measured by scanning electron microscopy (SEM), and  $V_{\rm th}$  is the threshold voltage. The gate capacitance can be approximated as  $C_{\rm g} = (1/\tilde{C}_{\rm ox} + 1/\tilde{C}_{\rm InAs} + 1/C_{\rm Q})^{-1}$ , where  $C_{\rm ox}$  is the gate oxide capacitance,  $C_{InAs}$  is the capacitance of the InAs cap layer, and  $C_0$  is the quantum capacitance. Based on parallel plate capacitance–voltage (C–V) measurements,  $C_{ox}$  is ~6.9 ×  $10^{-8}$  F/cm<sup>2</sup> for the 50 nm-thick SiO<sub>2</sub> back-gate dielectric. The detailed calculations of  $C_Q$  and  $C_{InAs}$  are presented in the Supporting Information. For back-gated devices with relatively thick oxides,  $C_{\rm ox} \ll C_{\rm Q}$  and  $C_{\rm InAs}$ , therefore,  $C_{\rm g} \approx C_{\rm ox}$ . The device shows a peak effective mobility of ~820  $cm^2/(V s)$  at  $V_{\rm DS}$  = -0.1 V (Figure 3b). This hole mobility is better than those of strained  ${\rm \tilde{S}i}~({\sim}260~{\rm cm}^2/(V~s))^{20}$  and unstrained Ge p-FETs  $(\sim 250 \text{ cm}^2/(\text{V s}))^{21}$  and comparable to strained 15 nm-thick Ge  $(\sim 1000 \text{ cm}^2/(\text{V s}))^{21}$  and strained buried 12.5 nm-thick InGaSb on III–V substrates ( $\sim 1000 \text{ cm}^2/(\text{V s})$ ).<sup>8</sup>

The strain of InGaSb in the InAs/InGaSb/InAs stack layer is calculated to be ~0.65% compressive strain for  $T_{InGaSb}$  = 15 nm and up to ~1.05% compressive strain for  $T_{\text{InGaSb}}$  = 7 nm. For the strain calculations, the lattice constants of InGaSb and InAs cladding layers in the heterostructure are assumed to be identical with a net internal force of zero. Due to the smaller bulk lattice constant of InAs, the InGaSb is compressed, while the InAs cladding layers are stretched. The thickness ratio of the InGaSb and InAs layers affects the final strain in each layer. By controlling the strain, further improvement of mobility may be possible.<sup>8,9</sup> Next, the effect of  $T_{InGaSb}$  on the electrical properties of the p-FETs was examined by keeping all other parameters constant. As seen from Figure 3c, the peak effective mobility decreases with the decrease of InGaSb thickness (see Figure S3, Supporting Information for mobility histograms), which may be attributed to the enhanced surface scattering

**Figure 3.** Electrical properties of back-gated XOI p-FETs. (a) Experimental transfer characteristics of a back-gated p-FET (50 nm SiO<sub>2</sub> gate dielectric) consisting of a single NR with  $T_{InGaSb} = 15$  nm. The inset shows a schematic of the device. (b) The effective hole mobility as a function of the back-gate voltage for the same device, showing a peak mobility of ~820 cm<sup>2</sup>/(V s) at  $V_{DS} = -0.1$  V. (c) Peak effective mobility as a function of InGaSb thickness, showing mobility reduction with thickness miniaturization. (d) The ON-state resistance as a function of the channel length. A contact resistance of ~580  $\Omega \mu m$  (per S/D contact) is extracted. The inset shows an SEM image of a single NR contacted with multiple electrodes with different spacing used for the TLM studies.

rates for thinner layers where most of the transport takes place closer to the surface.<sup>22</sup> Note that, as compared to the InAs capped devices, the uncapped InGaSb p-FETs (initial thickness, 20 nm; final thickness after processing, 7.5 nm) exhibit a hole mobility of only 50 cm<sup>2</sup>/(V s) (Figure S2, Supporting Information), highlighting the importance of the ultrathin InAs cap in obtaining high-performance devices.

Low contact resistance is particularly important when exploring basic carrier transport properties and device performance limits of a new material system. To characterize the contact resistance of our devices, transfer length method  $(TLM)^{23}$  was utilized. Back-gated p-FETs with channel lengths of  $L = 1-7 \mu m$  (measured by scanning electron microscopy) were fabricated and the ON-resistance at a vertical field of  $V_{\rm GS} - V_{\rm th} = -15$  V was extracted. The y-intercept of the ON-resistance versus L (Figure 3d) is approximately equal to  $2R_c$ , where  $R_c$  is the resistance associated with each contact (i.e., S or D). A contact resistance of ~580  $\Omega\mu m$  is extracted, which is impressive given that both InAs and InGaSb layers are undoped. The low-resistance contacts for holes is enabled by (i) the ease of ohmic contact formation to the conduction band of InAs<sup>24</sup> and (ii) the type-III band alignment of InAs/InGaSb heterojunction<sup>19</sup> underneath the metal contacts. This presents a novel approach for contacting Sb-based semiconductors.<sup>10</sup>

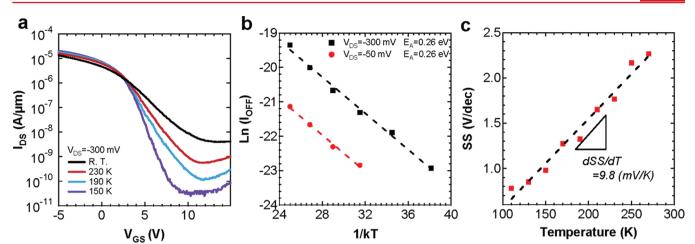

Figure 4a presents the temperature-dependent,  $I_{DS} - V_{GS}$ characteristics for a back-gated InAs/InGaSb/InAs XOI FET with  $T_{\text{InGaSb}}$  = 7 nm. As the temperature is lowered from room temperature to 100 K,  $I_{\rm OFF}$  decreases by >2 orders of magnitude. To further investigate the mechanism of the OFF-state leakage current generation, an Arrhenius plot of I<sub>OFF</sub> (chosen as the minimum current of the  $I_{DS} - V_{GS}$  plot) is shown in Figure 4b. An activation energy  $(E_A)$  of ~0.26 eV is extracted, which is close to half of the bandgap of In<sub>0.3</sub>Ga<sub>0.7</sub>Sb at both low and high fields of  $V_{\rm DS}$  = 50 and 300 mV. Such activation energy is typically attributed to trap-assisted tunneling and Shockley-Read-Hall generation/recombination. Presumably, trap states at the InAs/InGaSb interface<sup>25</sup> along with unintentional impurities incorporated during the growth result in the observed device leakage current. Thus, the performance of InAs capped InGaSb XOI may be further improved by optimizing the growth.

**Figure 4.** Temperature-dependent measurements of back-gated XOI p-FETs. (a)  $I_{DS} - V_{GS}$  characteristics as a function of temperature at  $V_{DS} = -0.1$  V for a device with  $T_{InGaSb} = 7$  nm. (b) OFF-state current as a function of 1/kT, showing an activation energy of ~0.26 eV. (c) Subthreshold swing vs temperature.

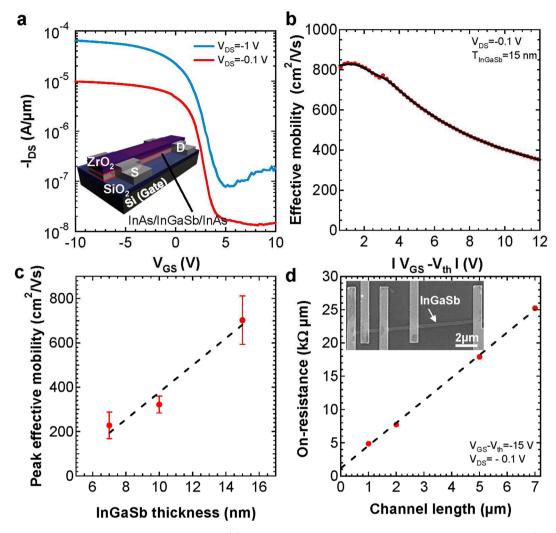

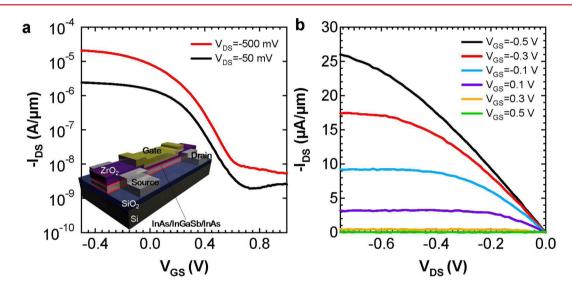

Figure 5. Top-gated XOI p-FETs. (a) Transfer and (b) output characteristics of a top-gated (10 nm ZrO<sub>2</sub> gate dielectric) InAs/InGaSb/InAs XOI FET with a channel length of ~6.1  $\mu$ m and  $T_{InGaSb} = 7$  nm. The Si substrate is grounded during the measurements.

To estimate the density of interface state traps  $(D_{it})$ , the change of the subthreshold swing (SS) with temperature was fitted with the analytical equation:

$$\frac{\mathrm{dSS}}{\mathrm{dT}} = \frac{2.3k}{q} \left[ 1 + \frac{C_{\mathrm{it}}}{C_{\mathrm{ox1}}} + \frac{C_{\mathrm{InGaSb}}}{C_{\mathrm{ox1}}} - \frac{\frac{C_{\mathrm{InGaSb}}}{C_{\mathrm{ox1}}C_{\mathrm{ox2}}}}{1 + \frac{C_{\mathrm{it}}}{C_{\mathrm{ox2}}} + \frac{C_{\mathrm{InGaSb}}}{C_{\mathrm{ox2}}}} \right]$$

where k is Boltzmann constant, q is the electron charge,  $C_{it} = q^2 D_{it}$  is the interface trap capacitance, and  $C_{InGaSb} = \varepsilon_{InGaSb} / T_{InGaSb}$  is the InGaSb body capacitance,  $\varepsilon_{InGaSb} = 16$  is the dielectric constant of InGaSb, and  $C_{ox1}$  and  $C_{ox2}$  are the capacitances of the active and nonactive gates, respectively (Figure 4c). To model the back gated devices, the equation was evaluated in the limit of  $C_{ox2} \rightarrow 0$  and  $C_{ox1}$  being the back-gate oxide capacitance. This analytical model is valid for an accumulation mode, thin body device,<sup>26</sup> such as the one studied here. The model assumes the carriers are directly beneath the gate, ignoring the finite distance from the surface due to quantization effects. Furthermore, the effect of the quantum capacitance is not considered, which is a valid assumption for our back-gated

FETs with a relatively thick back-gate oxide as  $C_Q \gg C_{ox}$ . The effect of body leakage was also ignored. The  $D_{it}$  of the device is determined to be ~1.4 × 10<sup>13</sup> cm<sup>-2</sup> eV<sup>-1</sup>, which is similar to most previous reports for Sb-based III–V FETs<sup>27</sup> but higher than the recent report of 3 × 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> by Nainani, et al.<sup>28</sup>

Letter

In a parallel approach,  $D_{\rm it}$  was extracted from C-V measurements using the conductance method.<sup>29</sup> For this study, topgated devices with the gate electrode underlapping the S/D contacts were fabricated with 10 nm of  $ZrO_2$  as the gate dielectric (see Supporting Information for detail). The  $D_{\rm it}$  using this technique is determined to be  $\sim 2 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>, which is consistent with the value obtained from the SS analysis technique presented above, further validating the results. This  $D_{\rm it}$  value is comparable to other previously fabricated Sb-based III–V FETs.<sup>27</sup> In the future, interface properties of the InGaSb XOI devices need to be further improved, for example, through the use of surface treatment prior to the gate stack formation and/or optimization of the gate dielectric layer.

Figure 5 shows the representative electrical characteristics of a top-gated p-FET with  $T_{InGaSb}$  = 7 nm. Here, the top-gate overlaps the *S*/*D* and the channel length is ~6.1  $\mu$ m. This long-channel

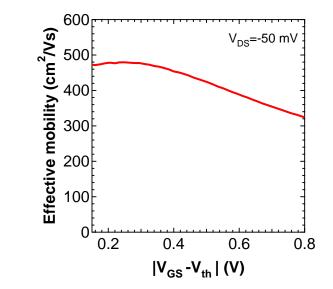

device at an operating voltage of  $V_{\rm DS} = \Delta V_{\rm GS} = 0.5$  displays  $I_{\rm ON}/$  $I_{\text{OFF}}$  of ~450 when using  $I_{\text{OFF}}$  = 10 nA. The subthreshold swing is SS ~ 130 mV/decade with a peak transconductance,  $g_{\rm m}$  of ~36  $\mu$ S/  $\mu m$  at  $V_{\rm DS} = -0.5$  V. The peak effective hole mobility is ~480 cm<sup>2</sup>/ (V s) (bias dependence of the mobility is shown in Figure S5, Supporting Information) based on the measured gate capacitance of  $\sim 9.5 \times 10^{-7}$  F/cm<sup>2</sup> directly obtained from C–V characterization (Figure S4b, Supporting Information). Note that based on the measured R<sub>2</sub>, the voltage drop at S/D contacts is ~5% at high gate fields, which would lead to a slight underestimation of the extracted mobility. This extracted mobility is higher than that of the backgated FETs of similar  $T_{InGaSb}$  (Figure 3c). The higher mobility of top-gated FETs is attributed to the lower surface scattering rates at the top surface of XOI as compared to the bottom interface. Specifically, the top dielectric  $(ZrO_2)$  is covalently bonded to the semiconductor surface since it is deposited by ALD, while the bottom dielectric layer (SiO<sub>2</sub>) is bonded by van der Waals interactions. Overall results here are comparable or better than previously reported InGaSb p-FETs fabricated on GaAs substrates.8 To test the stability of InGaSb XOI p-FETs, transfer characteristics were measured at  $V_{DS} = -0.5$  V over multiple cycles. As evident in Figure S6, Supporting Information, minimal change in the electrical properties is observed even after 2000 cycles of testing. The result is indicative of the high stability of the explored material system. Note that top-gated FETs with Al<sub>2</sub>O<sub>3</sub> gate dielectric (deposited by ALD) were also fabricated and tested but exhibited worse SS as compared to devices with ZrO<sub>2</sub> dielectrics, presumably due to lower interface qualities. Therefore, for all devices here, we utilized ZrO2 gate dielectrics.

In the future, short channel devices need to be explored to better benchmark the performance of InGaSb XOI p-FETs against those of the state-of-the-art Si MOSFETs and InSb quantum well FETs.<sup>18</sup> Scalability of the XOI processing needs to be explored in the future, although recent studies have demonstrated high-yield and large-area layer transfer of various semiconductor thin films onto hard and soft substrates.<sup>30</sup> In addition, materials and device optimization is needed to further enhance the performance of the devices, including the hole mobility. Specifically, the effects of cap material and thickness on the device properties require additional exploration. However, the results shown here present an effective hole mobility enhancement of  $\sim 5 \times$  over conventional Si p-MOSFETs. Importantly, the employed method may lead to the realization of complementary heterogeneous III-V electronics on Si substrates by utilizing high mobility InGaSb and InAs ultrathin layers as the p- and n-type materials, respectively, through a multistep transfer process.

## ASSOCIATED CONTENT

### **S** Supporting Information

Sample preparation and characterization of InGaSb without InAs capping layers, input parameters for the band diagram calculation, device variation of the mobility, stability of transfer characteristics, capacitance measurements, and  $D_{\rm it}$  extraction. This material is available free of charge via the Internet at http://pubs.acs.org.

### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: ajavey@eecs.berkeley.edu

## Present Address

•NanoSYD, Mads Clausen Institute, University of Southern Denmark, Sønderborg, Denmark.

### **Author Contributions**

$^{\nabla}$ These authors contributed equally.

### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

The device aspects of this work were funded by FCRP/MSD, NSF COINS, Intel, and NSF E3S Center. The materials characterization part of this work was supported by the Director, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division of the U.S. Department of Energy under contract no. DE-AC02-05CH11231. A.J. acknowledges a Sloan Research Fellowship, NSF CAREER Award, and support from the World Class University program at Sunchon National University. Y.-L.C. acknowledges support from the National Science Council, Taiwan, through grant no. NSC 98-2112-M-007-025-MY3. R.K. and M.M. acknowledge an NSF Graduate Fellowship and a postdoctoral fellowship from the Danish Research Council for Technology and Production Sciences, respectively.

## REFERENCES

(1) Kim, D.-H.; del Alamo, J. A. IEEE Trans. Electron Devices 2010, 57, 1504–1511.

(2) Heyns, M.; Tsai, W. MRS Bull. 2009, 34, 485-488.

(3) Bennett, B. R.; Ancona, M. G.; Boos, J. B. MRS Bull. 2009, 34, 530-536.

(4) Xuan, Y.; Wu, Y. Q.; Shen, T.; Yang, T.; Ye, P. D. *IEDM Tech. Dig.* 2007, 637–640.

(5) Radosavljevic, M.; Chu-Kung, B.; Corcoran, S.; Dewey, G.; Hudait, M. K.; Fastenau, J. M.; Kavalieros, J.; Liu, W. K.; Lubyshev, D.; Metz, M.; Millard, K.; Mukherjee, N.; Rachmady, W.; Shah, U.; Chau, R. *IEEE IEDM Tech. Digest* **2009**, 319–322.

(6) Balakrishnan, G.; Huang, S. H.; Khoshakhlagh, A.; Jallipalli, A.; Rotella, P.; Amtout, A.; Krishna, S.; Haines, C. P.; Dawson, L. R.; Huffaker, D. L. *Electron. Lett.* **2006**, *42*, 350–351.

(7) Yonezu, H. Semicond. Sci. Technol. 2002, 17, 762-768.

(8) Nainani, A.; Irisawa, T.; Yuan, Z.; Sun, Y.; Krishnamohan, T.; Reason, M.; Bennett, B. R.; Boos, J. B.; Ancona, M. G.; Nishi, Y.; Saraswat, K. C. *IEDM Tech. Dig.* **2010**, 138–141.

(9) Bennet, B. R.; Ancona, M. G.; Boos, J. B.; Shanabrook, V. Appl. Phys. Lett. 2007, 91, 042104.

(10) Xia, L.; Boos, J. B.; Bennett, B. R.; Ancona, M. G.; del Alamo, J. A. *Appl. Phys. Lett.* **2011**, *98*, 053505.

(11) Yoon, J.; Jo, S.; Chun, I. S.; Jung, I.; Kim, H.-S.; Meitl, M.; Menard, E.; Li, X.; Coleman, J. J.; Paik, U.; Rogers, J. A. *Nature* **2010**, 465, 329–333.

(12) Meitl, M. A.; Zhu, Z.-T.; Kumar, V.; Lee, K. J.; Feng, X.; Huang, Y. Y.; Adesida, I.; Nuzzo, R. G.; Rogers, J. A. *Nat. Mater.* **2006**, *5*, 33–38.

(13) Kim, H.; Brueckner, E.; Song, J.; Li, J.; Kim, S.; Lu, C.; Sulkin, J.; Choquette, K.; Huang, Y.; Nuzzo, R. G.; Rogers, J. A. *Proc. Natl. Acad. Sci. U.S.A.* **2011**, *108*, 10072–10077.

(14) Ko, H.; Takei, K.; Kapadia, R.; Chuang, S.; Fang, H.; Leu, P. W.; Ganapathi, K.; Plis, E.; Kim, H. S.; Chen, S.-Y.; Madsen, M.; Ford, A. C.; Chueh, Y.-L.; Krishna, S.; Salahuddin, S; Javey, A. *Nature* **2010**, 468, 286–289.

(15) Ford, A. C.; Yeung, C. W.; Chuang, S.; Kim, H. S.; Plis, E.; Krishna, S.; Hu, C.; Javey, A. *Appl. Phys. Lett.* **2011**, *98*, 113105.

(16) Yokoyama, M.; Yasuda, T.; Takagi, H.; Miyata, N.; Urabe, Y.; Ishii, H.; Yamada, H.; Fukuhara, N.; Hata, M.; Sugiyama, M.; Nakano, Y.; Takenaka, M.; Takagi, S. *Appl. Phys. Lett.* **2010**, *96*, 142106.

### **Nano Letters**

(17) Madsen, M.; Takei, K.; Kapadia, R.; Fang, H.; Ko, H.; Takahashi, T.; Ford, A. C.; Lee, M. H.; Javey, A. *Adv. Mater.* **2011**, *23*, 3115.

(18) Radosavljevic, M.; Ashley, T.; Andreev, A.; Coomber, S. D.; Dewey, G.; Emeny, M. T.; Fearn, M.; Hayes, D. G.; Hilton, K. P.; Hudait, M. K.; Jefferies, R.; Martin, T.; Pillarisetty, R.; Rachmady, W.; Rakshit, T.; Smith, S. J.; Uren, M. J.; Wallis, D. J.; Wilding, P. J.; Chau, R. *IEDM Tech. Dig.* **2008**, 1–4.

(19) Vizbaras, K.; Torpe, M.; Arafin, S.; Amann, M.-C. Semicond. Sci. Technol. 2011, 26, 075021.

(20) Mizuno, T.; Takagi, S.; Sugiyama, N.; Satake, H.; Kurobe, A.; Toriumi, A. *IEEE Electron Device Lett.* **2000**, *21* (5), 230–232.

(21) Pillarisetty, R.; Chu-Kung, B.; Corcoran, S.; Dewey, G.; Kavalieros, J.; Kennel, H.; Kotlyar, R.; Le, V.; Lionberger, D.; Metz, M.; Mukherjee, N.; Nah, J.; Rachmady, W.; Radosavljevic, M.; Shah, U.; Taft, S.; Then, H.; Zelick, N.; Chau, R. *IEDM Tech. Dig.* **2010**, 150–153.

(22) Takei, K.; Fang, H.; Kumar, S. B.; Kapadia, R.; Gao, Q.; Madsen, M.; Kim, H. S.; Liu, C.-H.; Chueh, Y.-L.; Plis, E.; Krishna, S.; Bechtel, H. A.; Guo, J.; Javey, A. *Nano Lett.* **2011**, *11*, 5008–5012.

(23) Xia, F.; Perebeinos, V.; Lin, Y.; Wu, Y.; Avouris, P. Nat. Nanotechnol. 2011, 6, 179–184.

(24) Chueh, Y.-L.; Ford, A. C.; Ho, J. C.; Jacobson, Z. A.; Fan, Z.; Chen, C.-Y.; Chou, L.-J.; Javey, A. *Nano Lett.* **2008**, *8*, 4528–4533.

(25) Zborowski, J. T.; Fan, W. C.; Golding, T. D.; Vigliante, A.; Chow, P. C.; Shih, H. D.; Anthony, J. M. J. Appl. Phys. **1992**, 71, 5908–5912.

(26) Colingea, J. P.; Flandre, D.; Van de Wielea, F. Solid-State Electron. 1994, 37, 289-294.

(27) Xu, M.; Wang, R.; Ye, P. D. *IEEE Electron Devices Lett.* 2011, 32, 883–885.

(28) Nainani, A.; Irisawa, T.; Yuan, Z.; Bennet, B. R.; Brad Boos, J.; Nishi, Y.; Saraswat, K. C. *IEEE Trans. Electron Devices* **2011**, *58*, 3407–3415.

(29) Nicollian, E. H.; Goetzberger, A. Appl. Phys. Lett. 1967, 10, 60-63.

(30) Rogers, J. A. Nature 2010, 468, 177-178.

## Nanoscale InGaSb heterostructure membranes on Si substrates for high hole mobility transistors

Kuniharu Takei<sup>1,2,3,†</sup>, Morten Madsen<sup>1,2,3,†,‡</sup>, Hui Fang<sup>1,2,3</sup>, Rehan Kapadia<sup>1,2,3</sup>, Steven Chuang<sup>1,2,3</sup>, Ha Sul Kim<sup>1,2,3</sup>, Chin-Hung Liu<sup>5</sup>, E. Plis<sup>4</sup>, Junghyo Nah<sup>1,2,3</sup>, Sanjay Krishna<sup>4</sup>, Yu-Lun Chueh<sup>5</sup>, Jing Guo<sup>6</sup> and Ali Javey<sup>1,2,3,\*</sup>

<sup>1</sup> Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, 94720

<sup>2</sup> Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

<sup>3</sup> Berkeley Sensor and Actuator Center, University of California, Berkeley, CA, 94720

<sup>4</sup> Electrical and Computer Engineering, University of New Mexico, Albuquerque, NM, 87106

<sup>5</sup> Materials Science and Engineering, National Tsing Hua University, Hsinchu 30013, Taiwan

<sup>6</sup> Electrical and Computer Engineering, University of Florida, Gainesville, FL, 32611

\* Corresponding author: <u>ajavey@eecs.berkeley.edu</u>

*† These authors contributed equally.*

*‡ Present address: NanoSYD, Mads Clausen Institute, University of Southern Denmark, Sønderborg, Denmark.*

## **Supporting Information**

## Sample preparation

Polymethylmethacrylate (PMMA):S1805 (70:30 volume ratio) line-patterns with a pitch and width of ~840 nm and ~350 nm, respectively, were lithographically formed on the MBE grown source substrates, followed by the wet etching of the InAs/InGaSb/InAs stack. Specifically, for the InAs layers, a mixture of citric acid (1g/mL in DI H<sub>2</sub>O) and hydrogen peroxide (30%) at a volume ratio of (1:20) was used (etch rate,  $\sim 1 \text{ nm/sec}$ ), whereas for the InGaSb layer, a hydrochloric acid (3.7% in DI H<sub>2</sub>O) and hydrogen peroxide (30%) mixture at a volume ratio of (200:1) was used (etch rate, ~1 nm/sec). Next, the NRs were partially released from the source wafer through the selective wet etching of the AlGaSb sacrificial layer in NH4OH (1.5 % in DI H2O; etch rate, ~1.8 nm/min). The partially released NRs were picked and transferred to a PDMS (~2 mm thick) slab. A 10 sec HF (1:50 in DI H<sub>2</sub>O) treatment ensures a high quality interface between InAs and SiO<sub>2</sub> by removing any residual AlGaSb from the back surface of the NRs. Subsequently, the layers were transferred onto a Si/SiO<sub>2</sub> substrate by the direct contact of PDMS onto the receiver substrate. Finally, the PMMA/S1805 resist layer was stripped in acetone. Note that the In<sub>0.3</sub>Ga<sub>0.7</sub>Sb composition is determined after MBE growth using Refection High Energy Electron Diffraction (RHEED) oscillations followed by X-ray measurements on calibration structures.

During device processing, ZrO<sub>2</sub> was deposited on the top surface of InAs/InGaSb/InAs XOI layers by atomic layer deposition at 130 °C by using tetrakis(ethylmethylamido)zirconium precursor and water. The deposition rate was ~1.1Å/cycle. Subsequently, forming gas anneal (5 % H<sub>2</sub> in Ar) at 130 °C for 30 min was performed. The forming gas anneal was found to be critical in improving the InAs/high-κ interface quality, and resulted in a lower *SS*.

## TEM imaging of uncapped InGaSb XOI

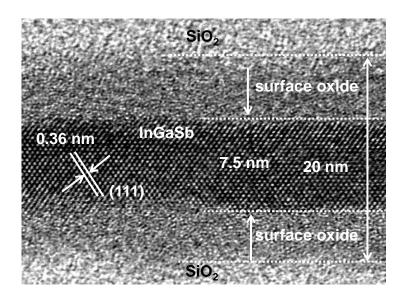

Figure S1 shows a TEM image of uncapped (i.e., without InAs cladding layers)  $In_{0.3}Ga_{0.7}Sb$  XOI, with an original (as-grown) InGaSb thickness of ~20 nm. Due to the high chemical reactivity of InGaSb, the surface is oxidized by up to ~6 nm on each side during the XOI processing, resulting in a final active layer thickness of ~7.5 nm.

Figure S1. A cross-sectional TEM image of an uncapped InGaSb XOI.

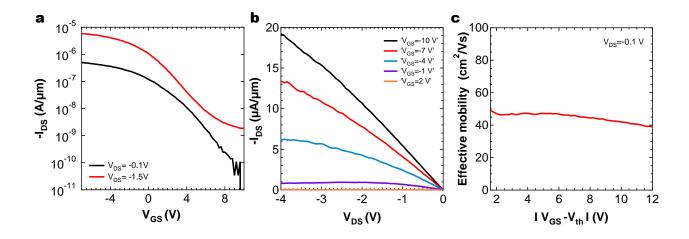

## Electrical characteristics of uncapped InGaSb XOI p-FETs

Representative electrical properties of back-gated, uncapped InGaSb XOI *p*-FETs (active layer thickness of ~7.5 nm with ~6 nm of native oxide on each side) are shown in Fig. S2. After device fabrication, ~8 nm ZrO<sub>2</sub> was deposited by ALD as an encapsulation layer. The extracted peak effective mobility is ~ 50 cm<sup>2</sup>/Vs, which is 3-4x lower than that of 7 nm-thick InGaSb heterostructure XOI *p*-FETs with InAs cap layers ( $\mu_p$ ~200 cm<sup>2</sup>/Vs, Fig. 3c).

**Figure S2.** Electrical transport properties of a back-gated InGaSb *p*-FET *without* InAs cap layers. The channel length for this device is ~5.5  $\mu$ m. **a**, Transfer characteristics at  $V_{DS}$ =-0.1 and -1.5 V, and **b**, I<sub>DS</sub>-V<sub>DS</sub> curves at different back-gate voltages. **c**, Effective hole mobility as a function of the gate field at  $V_{DS}$ =-0.1 V.

## Input parameters for the band structure calculations

Conduction band masses for the band diagram calculation using Nextnano are  $0.026m_0$ ,  $0.039m_0$  and  $0.0135m_0$  for InAs, GaSb and InSb, respectively, where  $m_0$  is free electron mass. To match with  $In_{0.3}Ga_{0.7}Sb$ , the mass was calculated based on the each mass value of GaSb and InSb by Nextnano.

## Device-to-Device Variation of the Mobility of InAs/InGaSb/InAs XOI p-FETs

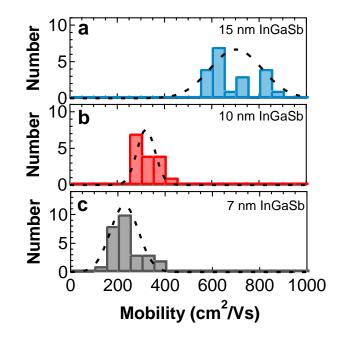

**Figure S3**. Histogram plots of the peak effective hole mobility of **a**, 15 nm-, **b**, 10 nm- and **c**, 7 nm-thick InGaSb back-gated FETs at  $V_{DS}$ =-100 mV. Standard deviation  $\sigma$  is ~109, 38 and 60 cm<sup>2</sup>/Vs for  $T_{InGaAs}$  of 15, 10 and 7 nm, respectively.

## Capacitance-voltage and *Gp/w*-frequency measurements

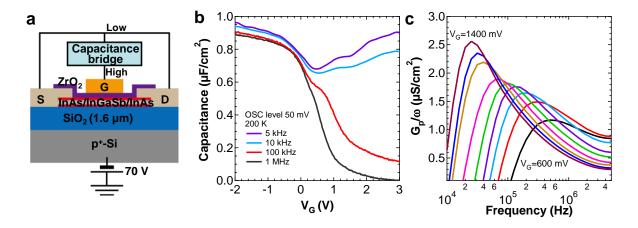

In conventional MOSFETs, the body and the S/D contacts are of different polarity, and the ON-state of the device corresponds to the gate voltage regime at which the body is inverted (i.e., inversion regime). In contrast, in the InGaSb XOI p-FETs explored here, the body is p-type and the contacts provide the direct injection of holes into the body. Thereby, the ON-state of the device corresponds to the accumulation regime and the device is OFF under the inversion mode. Thus, although *C-V* characteristics can be measured, direct extraction of the charge density is not possible in the InGaSb XOI FETs. However, through *C-V* and conductance-frequency (*G-f*) measurements, the total gate capacitance,  $C_g$ , and  $D_{it}$  values can be extracted, both of which are valuable device characterization parameters. Specifically, from the measured gate capacitance, the mobility of the XOI devices can be accurately assessed while the extracted  $D_{it}$  values provide insight into the interface quality.

The capacitance-voltage (*C*-*V*) characteristics of top-gated InGaSb XOI devices were measured between the gate (G) and source/drain (S/D) electrodes at 200 K (Fig. S4). Here,  $T_{InGaSb}$ =7 nm, the S/D spacing is ~5 µm, the gate length is ~3.2 µm, the top dielectric layer is ~10 nm-thick ZrO<sub>2</sub>, and the bottom oxide is ~1.6 µm-thick SiO<sub>2</sub>. An underlapped gate geometry was used to reduce the parasitic capacitances between the G and S/D electrodes. To reduce the series resistance of underlapped regions, a global back gate bias of -70 V was applied to the p+ Si substrate during the *C*-*V* and *G*-*f* measurements. Figure S4b shows *C*-*V* characteristics of the device at different frequencies from 5 kHz to 1 MHz. The gate capacitance in the accumulation regime (i.e., ON-state;  $V_g$ =-2V) was measured to be  $C_g \sim 9.5 \times 10^{-7}$  F/cm<sup>2</sup> based on the lowfrequency (5 kHz) *C*-*V* data (Fig. S4b). This capacitance value was used to extract the effective mobility of the top-gate devices from the I-V measurements (Fig. S5). The behavior in the accumulation, depletion and inversion regions of the measured *C*-V (Fig. S4b) is discussed in the following text. The dispersion in accumulation can be accounted for by the frequency dispersion of the dielectric constant of InAs and InGaSb. The gate capacitance in strong accumulation can be approximated as  $C_{\rm g} = (1/C_{\rm ZrO2} + 1/C_{\rm InAs} + 1/C_{\rm Q-DOS} + 1/C_{\rm Q-cent})^{-1}$ , where the quantum capacitance,  $C_{\rm Q-DOS}$ , arises from the density-of-state (DOS) capacitance, and  $C_{\rm Q-cent}$ , arises from the charge centroid capacitance. For a single hole subband,  $C_{\rm Q-DOS}$  is calculated from dQ/dE<sub>f</sub>, where  $Q = \int_{-\infty}^{E_v} g(E) d(E) dE$ , g(E) is the 2-D density of states, and f(E) is the Fermi function. The capacitance is calculated to be  $C_{\rm Q-DOS} \sim 2.7 \times 10^{-5}$  F/cm<sup>2</sup>. Using the SCHRED simulator, the hole charge centroid,  $t_{\rm cent}$ , was calculated to be  $\sim 1.5$  nm from the top interface. Using a parallel plate approximation with  $\varepsilon_{\rm InGaSb} = 16.03$ ,  $C_{\rm Q-cent} = \frac{\varepsilon_{InGaSb} \varepsilon_0}{t_{cent}} \sim 9.5 \times 10^{-6} \text{ F/cm}^2$ . The capacitance of the ZrO<sub>2</sub>/InAs stack was calculated with  $t_{\rm InAs} = \frac{\varepsilon_{InGaSb} \varepsilon_0}{t_{cent}}$ .

2.5 nm,  $\varepsilon_{\ln As}=15.1$ ,  $t_{ZrO2} = 10$  nm,  $\varepsilon_{ZrO2}=16$ . The series combination of the  $ZrO_2/InAs$  gate stack with  $C_{Q-cent}$  and  $C_{Q-DOS}$  gives a calculated low-frequency  $C_g$  of  $9.7 \times 10^{-7}$  F/cm<sup>2</sup> in strong accumulation, which is in good agreement with the measured capacitance value of ~9.5×10<sup>-7</sup> F/cm<sup>2</sup> (Fig. S4b). In the inversion region, the dispersion is due to the lack of a contact to the conduction band. Thus, as in a conventional MOS capacitor, the electrons are unable to respond to the high-frequency signal, causing the dispersion observed. The feature at  $V_g$  ~1.5 V is attributed to inversion of the heavily quantized InAs capping layer.

In addition, *G-f* measurements were also carried out to extract  $D_{it}$  values for the present device using the conductance method<sup>1</sup>. To extract  $D_{it}$  from the measured conductance ( $G_m$ ) and capacitance ( $C_m$ ) values, we first extract the series resistance ( $R_s$ ) by using equation (1) as a function of excitation frequency  $\omega = 2\pi f$ .

(1)

$$R_s = \frac{G_{ma}}{G_{ma}^2 + \omega^2 C_{ma}^2}$$

Here,  $C_{ma}$  and  $G_{ma}$  are the measured capacitance and conductance in strong accumulation respectively. Then, the series resistance correction factor (a) was calculated using equation (2).

(2)

$$a = G_m - (G_m^2 + \omega^2 C_m^2) R_s$$

The corrected conductance  $(G_c)$  and capacitance  $(C_c)$  were then calculated from equations (3) and (4), respectively.

(3)

$$G_{c} = \frac{(G_{m}^{2} + \omega^{2}C_{m}^{2})a}{a^{2} + \omega^{2}C_{m}^{2}}$$

$$C_{c} = \frac{(G_{m}^{2} + \omega^{2}C_{m}^{2})C_{m}}{a^{2} + \omega^{2}C_{m}^{2}}$$

(4)

Finally,  $G_p/\omega$  was calculated using equation (5), and the  $D_{it}$  was extracted by taking the maximum  $G_p/\omega$  for a given gate voltage in equation (6).

(5)

$$\frac{G_p}{\omega} = \frac{\omega G_c C_{ox}^2}{G_c^2 + \omega^2 (C_{ox} - C_c)^2}$$

$$D_{it} = \frac{2.5}{g} \frac{G_p}{\omega}$$

(6)

~

Figure S4c shows the calculated

$$G_p/\omega$$

vs frequency. The  $D_{it}$  of the device is extracted to be  $\sim 2 \times 10^{13} \text{ cm}^2/\text{Vs}$ .

**Figure S4. a**, Device schematic used for the C-V and conductance measurements. **b**, Measured *C-V* curves at different frequencies (5 kHz-1 MHz) at a sample temperature of 200 K. **c**,  $G_p/\omega f$  curves used to extract the surface state D<sub>it</sub>.

## Effective Hole Mobility of Top-Gated InGaAs XOI FETs (TInGaSb = 7 nm)

**Figure S5.** Effective mobility as a function of the gate field for a 7 nm-thick InGaSb XOI *p*-FET. The result is for the same device shown in Fig. 5.

## Stability of top-gated InGaSb XOI FETs

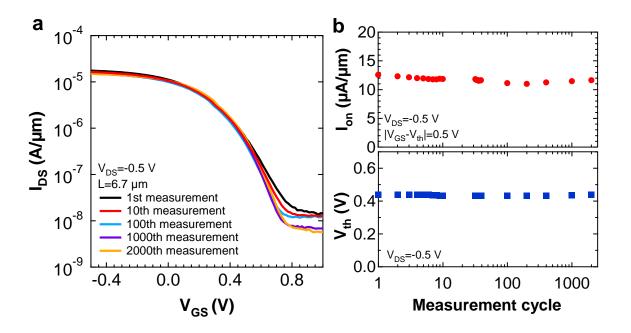

Figure S6 shows the  $I_{DS}$ - $V_{GS}$  curves of a 7 nm-thick InAs/InGaSb/InAs top-gated FET after multiple cycles of measurement, up to 2000 times, at  $V_{DS}$ =-0.5 V. The device is highly stable with minimal change in the device characteristics over multiple cycles of operation.

**Figure S6**. **a**, Transfer characteristics of a top-gated device after multiple cycles of measurements at  $V_{DS}$ =-0.5 V. **b**,  $I_{ON}$  at  $|V_{GS}-V_{th}|$ =0.5 V and **c**,  $V_{th}$  as a function of measurement cycle at  $V_{DS}$ =-0.5 V.

## **References**

1. Nicollian, E. H.; Goetzberger, A. Appl. Phys. Lett. 1967, 10, 60-63.