# NANULETTERS

# **Carbon Nanotube Active-Matrix Backplanes for Conformal Electronics** and Sensors

Toshitake Takahashi,<sup>†,‡,§</sup> Kuniharu Takei,<sup>†,‡,§</sup> Andrew G. Gillies,<sup>||</sup> Ronald S. Fearing,<sup>†</sup> and Ali Javey<sup>\*,†,‡,§</sup>

<sup>+</sup>Electrical Engineering and Computer Sciences and <sup>‡</sup>Berkeley Sensor and Actuator Center, University of California, Berkeley, California 94702, United States

<sup>§</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, United States

<sup>I</sup>Mechanical Engineering, University of California, Berkeley, California 94702, United States

#### Supporting Information

ABSTRACT: In this paper, we report a promising approach for fabricating large-scale flexible and stretchable electronics using a semiconductor-enriched carbon nanotube solution. Uniform semiconducting nanotube networks with superb electrical properties (mobility of  $\sim 20 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and  $I_{\text{ON}}/I_{\text{OFF}}$  of  $\sim 10^4$ ) are obtained on polyimide substrates. The substrate is made stretchable by laser cutting a honeycomb mesh structure, which combined with nanotubenetwork transistors enables highly robust conformal electronic devices with minimal device-to-device stochastic variations. The utility of this device concept is demonstrated by fabricating an active-matrix back-

plane ( $12 \times 8$  pixels, physical size of  $6 \times 4$  cm<sup>2</sup>) for pressure mapping using a pressure sensitive rubber as the sensor element.

KEYWORDS: Carbon nanotube electronics, macroelectronics, artificial electronic skin, stretchable sensors, semiconductorenriched nanotubes, flexible backplane

In recent years, flexible and stretchable electronics have been intensively explored for enabling new applications otherwise unachievable with the conventional Si technology.<sup>1-3</sup> A wide range of active channel materials have been explored, including organics;<sup>4–9</sup> amorphous,<sup>10,11</sup> poly-<sup>12,13</sup> and single-crystalline semiconductors in the shape of thin films and strips;<sup>14,15</sup> printed semiconducting nanowires (NWs);<sup>16–18</sup> and single-walled carbon nanotubes (SWNTs).<sup>19,20</sup> Each of these material systems presents unique opportunities and challenges for large-area electronics. For instance, randomly deposited films of SWNTs are attractive candidates given their high carrier mobility, high chemical stability, ability to deposit through solution processing, and superb mechanical properties such as high bendability.<sup>21–23</sup> A challenge, however, has been to fabricate devices with high ON/OFF current ratio, given that nanotube networks often consist of a mixture of semiconductor and metallic SWNTs.<sup>24</sup> In this regard, highly semiconductor-enriched (99%) SWNTs have been recently reported and commercialized through the use of a density gradient ultracentrifugation technique.<sup>25,26</sup> This development has allowed for the fabrication of high performance SWNT thin-film transistors (TFTs) that exhibit high  $I_{\rm ON}/I_{\rm OFF}$  (>10<sup>2</sup>) and mobility (>10 cm<sup>2</sup>/(V s)) on rigid Si substrates.<sup>27–30</sup> This presents an important advance in the field and could result in the development of highly scalable and low-cost electronics with performances drastically superior to those of conventional organics or a-Si. Here, we extend on this work and report the development of mechanically flexible and stretchable active-matrix backplanes based on semiconductor-enriched SWNT networks.

We demonstrate fully passivated and highly uniform SWNT TFT arrays, covering large areas of  $\sim$ 7.5 cm  $\times$  7.5 cm. As an example system, we utilize this active-matrix backplane for an artificial electronic skin (e-skin) device,  $^{8,9,16,31}$  capable of spatial mapping of touch.

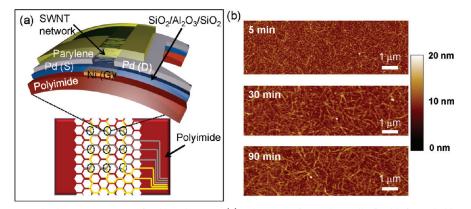

The device schematic of a mechanically deformable activematrix backplane based on SWNT TFTs is shown in Figure 1a. A 24  $\mu$ m thick polyimide (PI) layer (PI-2525, HD MicroSystem) is used as the substrate. First, the PI is spin-coated twice (2000 rpm for 1 min) on a Si/SiO<sub>2</sub> handling 4 in. wafer, followed by Ni gate electrode deposition by thermal evaporation. The gate oxide consists of three layers with a 20 nm thick Al<sub>2</sub>O<sub>3</sub> layer deposited by atomic layer deposition (ALD) sandwiched between electron-beam deposited SiO<sub>x</sub> layers (thicknesses, 10 and 15 nm on bottom and top, respectively). The bottom  $SiO_x$  layer is used to enable nucleation of ALD Al<sub>2</sub>O<sub>3</sub> on the substrate, while the top  $SiO_x$  layer is used for adhesion of SWNTs. Note that it is observed that SWNTs are highly nonsticky to ALD Al<sub>2</sub>O<sub>3</sub> surfaces, presumably due to fixed charges in the as-deposited alumina layer. To deposit highly dense and uniform SWNTs networks, the  $SiO_x$  surface is modified with poly-L-lysine by solution casting for  $\sim$ 5 min followed by a rinse with DI water. In this study, we use as-received 99% semiconductor enriched SWNT solution (IsoNanotubes-S from NanoIntegris, Inc.)

| Received:  | September 7, 2011 |

|------------|-------------------|

| Revised:   | October 16, 2011  |

| Published: | November 03, 2011 |

pubs.acs.org/NanoLett

**Figure 1.** Semiconductor-enriched SWNT TFTs on flexible substrates. (a) Schematic of a mechanically flexible/stretchable active-matrix back-plane ( $6 \times 4 \text{ cm}^2$  with  $12 \times 8$  pixel array) based on SWNT TFTs, and an expanded schematic of a single TFT. (b) Atomic force microscopy images of SWNT networks on a PI substrate, showing that the density can be controlled by the nanotube deposition time (5, 30, and 90 min; top to bottom, respectively). Average length of nanotubes is  $\sim 0.8 \mu$ m.

without any densification. SWNTs were then deposited by solution casting followed by rinse with DI water.

Figure 1b shows the atomic force microscopy (AFM) images of the SWNT coated substrates for three different nanotube deposition times. As evident, the density of SWNTs on the evaporated SiO<sub>x</sub> depends on the deposition time and is estimated to be  $\sim$ 6, 8, and 10 SWNTs/ $\mu$ m for the deposition time of 5, 30, and 90 min, respectively (Figure 1b). It should be noted that the density of SWNTs as a function of deposition time is highly dependent on the particular surface being explored. For instance, higher densities of SWNTs with higher bundling probability are observed for similar deposition times on thermally grown SiO<sub>2</sub> layers (see Supporting Information, Figure S2). Furthermore, the density depends on the surface functionalization of the substrate and the nanotube surfactants (Supporting Information, Figure S1). Next, vacuum annealing at 200 °C for 1 h is performed to remove surfactant residues. This annealing process is essential to improve both the transconductance and  $I_{ON}/I_{OFF}$ of the devices (see Supporting Information, Figure S3). Pd (thickness,  $\sim$ 35 nm) source/drain (S/D) electrodes are then patterned using photolithography, metallization, and lift-off to enable ohmic contacts to the valence band of nanotubes for hole transport.<sup>32</sup> Finally, the fabrication process is completed by encapsulating the active matrix with parylene-C ( $\sim$ 500 nm) to improve the mechanical robustness and chemical stability by removing environmental effects, including surface-absorbed water molecules (Figure 1a). Via contacts are made by pattern etching of parylene using photolithography and O<sub>2</sub> plasma etch. After the completion of the entire process, the PI layer is readily peeled off from the handling wafer, resulting in a mechanically flexible device. Here, after cutting the edge of the substrate with a razor blade, the PI layer is readily released due to the poor adhesion between PI and SiO2. During this process no breakage of the metal lines or active regions is observed due to the parylene encapsulation.

Figure 2a shows the transfer characteristics of SWNT TFTs measured at  $V_{\rm DS} = -5$  V for three different deposition times. For each condition, 30 devices with channel length of  $L \sim 3 \,\mu m$  and width of  $W \sim 250 \,\mu m$  are randomly chosen across a 4 in. substrate and measured to study the stochastic device-to-device fluctuation. Figure 2b-e shows the histograms of peak transconductance ( $g_m$ , unit width normalized), peak field-effect mobility ( $\mu$ ), log-scale  $I_{\rm ON}/I_{\rm OFF}$ , and the threshold voltage

Figure 2. Statistical variation of the electrical properties over a 4 in. PI substrate. (a) Transfer characteristics of SWNT TFTs at  $V_{\rm DS} = -5$  V for three different SWNT deposition times of 5, 30, and 90 min, corresponding to different nanotube densities. (b–e) Histograms of widthnormalized transconductance, peak field-effect mobility, log-scale of  $I_{\rm ON}/I_{\rm OFF}$ , and threshold voltage for each deposition condition. In (b,d), the devices are measured at  $V_{\rm DS} = -5$  V, and in (c,e) the devices are measured at  $V_{\rm DS} = -50$  mV. (f) Peak field-effective mobility as a function of  $I_{\rm ON}/I_{\rm OFF}$  for various measured devices. Here, the channel length is  $\sim 3 \,\mu$ m and width is 250  $\mu$ m.

$(V_t)$  for each deposition condition. The transconductance and  $I_{\rm ON}/I_{\rm OFF}$  are measured at  $V_{\rm DS}$  = -5 V, and the mobility and

threshold voltage are measured at  $V_{\rm DS} = -50$  mV. Calculation of the gate oxide capacitance must be addressed in the case of the SWNT network device.<sup>33</sup> Here, the effect of electrostatic coupling between nanotubes is considered with the following equation:

$$C_{i} = \left\{ \frac{1}{2\pi\varepsilon} \ln \left[ \frac{\Lambda_{0}}{R} \frac{\sinh\left(\frac{\pi 2d}{\Lambda_{0}}\right)}{\pi} \right] + C_{Q}^{-1} \right\}^{-1} \Lambda_{0}^{-1}$$

where  $1/\Lambda_0$  is the density of nanotubes,  $C_Q = 4.0 \times 10^{-10}$  F/m is the quantum capacitance of nanotubes (refs 34 and 35), d is the oxide thickness, and R = 0.7 nm is the average radius of nanotubes. The calculated gate oxide capacitance values are  $2.45 \times 10^8$  F/cm<sup>2</sup>,  $3.16 \times 10^8$  F/cm<sup>2</sup>, and  $3.78 \times 10^8$  F/cm<sup>2</sup> for SWNT deposition time of 5, 30, and 90 min, respectively. The field-effect mobility can then be extracted as,  $\mu = (L/V_{DS}C_i)(g_m/W)$ . As the nanotube deposition time increases from 5 to 90 min, average peak  $g_{\rm m}$  increases from  $\sim 0.4$  to 1.5  $\mu {\rm S}/\mu {\rm m}$  at  $V_{\rm DS} = -5$  V, resulting in an increased hole mobility from ~18 to ~27 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. On the other hand,  $I_{\rm ON}/I_{\rm OFF}$  shows the opposite trend, decreasing as the nanotube density increases. This is due to the bundling of SWNTs that makes gate control less effective, causing increased OFF-currents. In addition, by increasing the nanotube density, the probability of a direct metallic interconnection between the S/D electrodes increases given that 1% of SWNTs in the solution are still metallic.<sup>29,30</sup> This point might be further improved in the future by using higher purity SWNTs and/or different surface chemistry. The relationship between mobility and  $I_{\rm ON}/I_{\rm OFF}$  is summarized in Figure 2f. Because of the 99% semiconductor-enriched SWNTs used in this work, a high mobility of  $\sim$ 20 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> is obtained without sacrificing  $I_{\rm ON}/I_{\rm OFF}$  (~10<sup>4</sup>) even for a relatively shorter channel length ( $\tilde{L} \sim 3 \,\mu m$ ). Our superior electrical properties compared to previous reports,<sup>30</sup> where the same purity of SWNTs (99%) are used, mainly comes from the process difference. In this work, the SiO<sub>2</sub> surface is modified with poly-L-lysine, as opposed to APTES in previous reports,<sup>30</sup> resulting in denser SWNT networks. And subsequent removal of surfactant residue by vacuum annealing improves the  $I_{\rm ON}/I_{\rm OFF}$  (see Supporting Information, Figure S3). Of particular importance, uniformity of the explored SWNT TFT technology on flexible substrates is impressive. Focusing on the 90 min deposition condition, the standard deviation for  $g_{\rm m}$ ,  $\mu$ ,  $\log(I_{\rm ON}/I_{\rm OFF})$ , and  $V_{\rm t}$  are ~11, 17, 11, and 3%, respectively.

The variations of the key performance metrics listed above are slightly larger than the state-of-the art organic materials<sup>36</sup> although the devices are processed in noncleanroom environment, but are sufficient for applications such as active-matrix backplanes. Of particular importance, a high mobility, such as those obtained here, is highly desired for lowering the operating voltage and the size (i.e., width) of the FETs. This presents a major advantage for the use of SWNT TFTs over their organic counterparts for use as the active matrix backplanes, although both are solution-processed. In addition, given the graphitic nature of SWNTs, they are highly robust and chemically stable, without degradation over time. These remarkable properties clearly set the advantage of semiconductor-enriched SWNT networks for large-area electronics. Here, we focus on the use of SWNT TFTs for mechanically flexible and stretchable backplanes using PI as the support substrate. These backplanes could

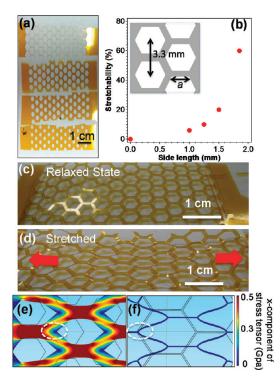

**Figure 3.** Stretchable PI substrates. (a) PI mesh substrate with four different side length of hexagonal holes (a = 1, 1.25, 1.5, and 1.85 mm, from bottom to top). (b) Stretchability as a function of the side length, a, of the hexagonal holes. Here, the period of holes is fixed at 3.3 mm as shown in the inset. Optical images of (c) relaxed and (d) stretched state of the PI substrate with a = 1.25 mm. Mechanical simulation of (e) a = 1.25 mm and (f) a = 1.85 mm mesh, when the substrate is stretched by 2 mm in the horizontal direction. The location where the active devices are placed is marked with the white circle.

serve for development of displays, sensor arrays and imagers, just to name a few examples.

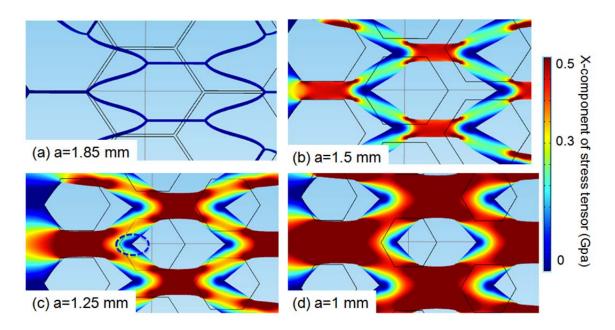

To obtain mechanically stretchable electronics, several approaches have been previously reported such as micro/nanostructures in "wavy" layouts and open mesh substrate geometries.<sup>9,37,38</sup> Here, to reduce process complexity and make the substrate more robust against unidirectional stretching, we utilize a honeycomb mesh structure, where an array of holes in the shape of hexagons are laser cut on a thin PI substrate with a fixed pitch of 3.3 mm and a varied hole side-length of a = 1 - 1.85 mm (Figure 3a). The mechanical stretchability of the PI mesh is then characterized as a function of *a* (Figure 3b). The stretchability is defined as the maximum engineering strain that the substrates can tolerate before failure (i.e., breakage). The stretchability increases from 0 to  $\sim$ 60% as the side length of the hexagonal holes increases from 0 to 1.85 mm. This observation is consistent with the mechanical simulations, where the induced stress is found to be reduced by increasing the hole size (Figure 3e,f and Figure S5). The unpatterned PI film is stiff and incapable of stretching. By cutting a honeycomb mesh pattern on the substrate, the enabled structure becomes stretchable because the PI bridges in-between the hexagonal holes can twist as evident from the optical images in Figure 3c,d. Because of a structural symmetry, the honeycomb mesh is invariant to every 60° rotation, so the same stretchability can be observed for those directions. The degree of stretchability and directionality can be further tuned in

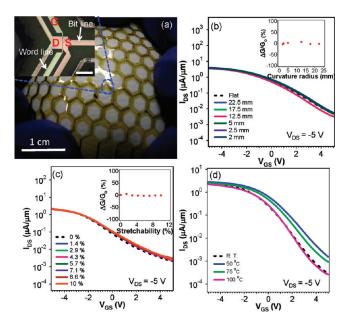

**Figure 4.** Mechanical robustness of SWNT TFTs on honeycomb patterned PI substrates. (a) Optical images of a stretchable device array, showing conformal coverage on a baseball. Expanded image of an active device area (corresponding to the TFT for a single pixel) is shown in the inset (scale bar is 200  $\mu$ m). Channel length and width are 5 and 200  $\mu$ m, respectively. (b) Transfer characteristics at  $V_{\rm DS} = -5$  V measured at various bending radius. The inset depicts  $\Delta G/G_0$  as a function of bending radius, showing minimal performance change even when bent down to 2 mm of bending radius (c) Transfer characteristic at  $V_{\rm DS} = -5$  V as a function of stretchability. The inset shows  $\Delta G/G_0$  as a function of stretchability. (d) Transfer characteristics at  $V_{\rm DS} = -5$  V as a function.

the future by either changing the hole size and/or optimizing the mesh design.

Next, the mechanical stability of SWNT TFT arrays on a honeycomb-structured PI substrate is studied. The PI substrate is laser cut into a honeycomb structure with a = 1.25 mm after fully encapsulating the TFTs with parylene. Figure 4a shows the honeycomb patterned PI substrate with SWNT TFT arrays conformably covering a baseball. Here, active devices with  $L \sim$ 5  $\mu$ m and  $W \sim$  200  $\mu$ m are placed on the bridge intersects of each hexagon as marked by blue circles in Figure 4a. The nanotube deposition time is 60 min, corresponding to  $\sim$ 9 SWNTs/ $\mu$ m. The transfer characteristics at  $V_{\rm DS}$  = -5 V as a function of radius of curvature are shown in Figure 4b. The device operates without noticeable degradation even when mechanically bent down to a 2 mm radius of curvature. In the inset of Figure 4b, the normalized change in the conductance,  $\Delta G/G_0$ , where  $\Delta G = G_0 - G$  and G and  $G_0$  are the conductance for bent and relaxed (that is curvature radius is infinity) states, respectively, is shown. This bendability comes from the proper device design that exploits the neutral bending plane of the substrate, the miniaturized dimensions of SWNTs, and the mechanical robustness of the SWNTs. Similarly, the transfer characteristics as a function of unidirectional stretching are shown in Figure 4c. Here, the substrate is pulled along its length while the TFTs are electrically measured. The device functions with no change for stretching up to  $\sim$ 3 mm displacement, corresponding to ~11.5% stretchability. The induced stress on stretching with 11.5% of stretchability is calculated using a finite-element method simulation (Comsol Multiphysics

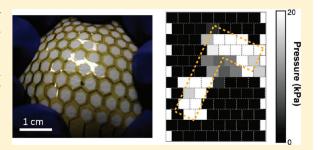

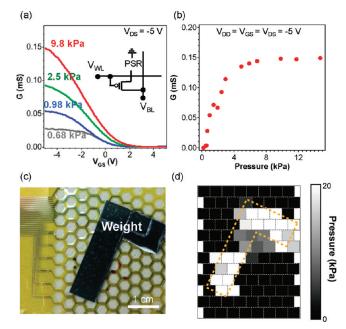

**Figure 5.** Artificial electronic-skin using SWNT TFT active matrix back-plane. (a) Transfer characteristics as a function of the normal applied pressure for a representative pixel. (b) Output conductance at  $V_{\rm DD} = V_{\rm GS} = V_{\rm DS} = -5$  V as a function of the applied normal pressure. (c) Optical image of a fully fabricated electrical skin sensor. An L-shaped object is placed on top. (d) The two-dimensional pressure mapping obtained from the L-shaped object in (c).

3.3) as shown in Figure 3e and Figure S5. It is clearly seen that most of the stress is introduced at the bridge regions, not on the active device regions.

Next, the thermal stability of the fully encapsulated SWNT TFTs is explored. The devices were heated in air from room temperature to 100 °C. Only a minimal change in  $V_t$  is observed (Figure 4d), which could be attributed to a slight change of the dielectric constant of the various layers used in the devices. The results here suggest that the TFT array technology presented here are not only uniform over large-areas, but exhibit superb mechanical and thermal properties, ideal for large-area conformal electronics.

To demonstrate the utility of the proposed device scheme, as an example system, SWNT TFT active matrix backplane is used for spatial pressure mapping, consisting of a  $12 \times 8$  (physical size of  $6 \times 4 \text{ cm}^2$ ) pixel array. Here, each pixel is actively controlled by a single TFT. The device effectively functions as an artificial electrical skin (e-skin), capable of detecting and mapping touch profiles.<sup>8,9,16</sup> For this purpose, a pressure sensitive rubber (PSR -PCR Technical, Japan) is laminated on top of the parylenepassivated back-plane. The drain of each transistor is electrically connected to the PSR that is then grounded by an aluminum foil. The source and gate electrodes of the TFTs are used as the bit and word lines, respectively. PSR is near insulating ( $\sim$ 30 Mohm) in its relaxed state. However, the resistivity decreases to <0.5 ohm/pixel by applying an external pressure of  $\sim$ 6 kPa due to the shortened tunneling path between the conducting carbon nanoparticles in the PSR. Figure 5a shows the output characteristics of a single pixel upon applying a normal pressure to the device. The pixel response at an operating voltage of  $V_{\rm DD}$  = -5 V is shown in Figure 5b. In the linear operation regime, the sensor sensitivity, S = dG/dP, is ~30  $\mu$ SkPa<sup>-1</sup>, which is a threefold improvement

compared with previous NW-based sensor<sup>4</sup> resulting from improved on-current of SWNT devices. In this e-skin layout, transistor channels and PSR are placed in series, but after a normal pressure of >6 kPa, the resistivity of PSR becomes negligible compared to the TFTs, thereby, resulting in the saturation of the pixel response. To show the functionality of the integrated e-skin, an "L"-shaped weight is placed on top of the sensor array with the normal pressure of  $\sim 15$  kPa (Figure 5c). The output conductance for each pixel is measured with the word and bit line voltages of  $V_{\rm WL}$  = -5 V and  $V_{\rm BL}$  = -1 V and is plotted to show the measured two-dimensional pressure mapping (Figure 5d). The defective pixels stem from processing issues such as inadequate lift-off. The enabled pressure mapping shown here demonstrates the utility of SWNT TFT arrays for active-matrix backplane of sensor arrays on mechanically deformable substrates. In the future, pixel density can be further improved by decreasing the size of both the SWNT active region and the contact region to PSR.

In conclusion, high-performance TFT arrays with a hole mobility of 20–30 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and respectable  $I_{\rm ON}/I_{\rm OFF} \sim 10^4$  are uniformly obtained on large-scale plastic substrates by solution processing of semiconductor-enriched SWNT networks. This solution-based approach can be potentially combined with inkjet printing of metal contacts to achieve lithography-free fabrication of low-cost flexible and stretchable electronics with superb electrical and mechanical properties. Notably, to achieve stretchability using robust PI substrates, a concept often used in the paper decoration industry was applied by proper laser cutting of the substrate. The back-plane technology explored here can be further expanded in the future by adding various sensor and/or other active device components to enable multifunctional artificial skins.

### ASSOCIATED CONTENT

**Supporting Information.** SWNT-network density as a function of surface treatment and deposition time; the effect of vacuum annealing on device properties; output characteristics of SWNT TFTs; mechanical simulations of honeycomb patterned structures. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

#### **Corresponding Author**

\*E-mail: ajavey@eecs.berkeley.edu.

#### ACKNOWLEDGMENT

This work was partially funded by NSF COINS, NSF CA-REER Award, and DARPA/DSO Maximum Mobility and Manipulation. The materials characterization part of this work was supported by was partially supported by the Director, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. A.J. acknowledges support from the World Class University program at Sunchon National University and a Sloan Fellowship.

#### REFERENCES

(1) Sekitani, T.; Someya, T. Adv. Mater. 2010, 22, 2228-2246.

(2) Kim, D. H.; Xiao, J.; Song, J.; Huang, Y.; Rogers, J. A. Adv. Mater. **2010**, *22*, 2108–2124.

(3) Wagner, S.; Lacour, S. P.; Jones, J.; Hsu, P. H. I.; Sturm, J. C.; Li, T.; Suo, Z. *Physica E* **2004**, *25*, 326–334.

(4) Rogers, J. A.; Bao, Z.; Baldwin, K.; Dodabalapur, A.; Crone, B.; Raju, V. R.; Kuck, V.; Katz, H.; Amundson, K.; Ewing, J.; Drzaic, P. *Proc. Natl. Acad. Sci. U.S.A.* **2001**, *98*, 4835.

(5) Forrest, S. F. Nature 2004, 428, 911.

(6) Gelinck, G. H.; Huitema, H. E. A.; van Veenendaal, E.; Cantatore, E.; Schrijnemakers, L.; van der Putten, J. B. P. H.; Genus, T. C. T.; Beenhakkers, M.; Giesbers, J. B.; Huisman, B. H.; Meijer, E. J.; Benito, E. M.; Touwslager, F. J.; Marsman, A. W.; van Rens, B. J. E.; de Leeuw, D. M. Nat. Mater. **2004**, *3*, 106.

(7) Klauk, H. Nature 2008, 451, 533.

(8) Someya, T.; Sekitani, T.; Iba, S.; Kato, Y.; Kawaguchi, H.; Sakurai, T. *Proc. Natl. Acad. Sci. U.S.A.* **2004**, *101*, 9966–9970.

(9) Someya, T.; Kato, Y.; Sekitani, T.; Iba, S.; Noguchi, Y.; Murase, Y.; Kawaguchi, H.; Sakurai, T. Proc. Natl. Acad. Sci. U.S.A. 2005, 102, 12321–12325.

(10) Gleskova, H.; Wagner, S. *IEEE Electron Device Lett.* **1999**, 20, 473–475.

(11) Thomasson, D. B.; Bonse, M.; Huang, J. R.; Wronski, C. R.; Jackson, T. N. *IEDM Tech. Dig.* **1998**, 253–256.

(12) Theiss, S. D.; Carey, P. G.; Smith, P. M.; Wickboldt, P.; Sigmon, T. W.; Tung, Y. J.; King, T.-J. *IEDM Tech. Dig.* **1998**, 257–260.

(13) Wang, S. C.; Yeh, C. F.; Huang, C. K.; Dai, Y. T. Jpn. J. Appl. Phys. 2003, 42, L1044–L1046.

(14) Kim., D. H.; Ahn, J. H.; Choi, W. M.; Kim, H. S.; Kim, T. H.;

Song, J.; Huang, Y. Y.; Liu, Z.; Lu, C.; Rogers, J. A. Science 2008, 320, 507.

(15) Sun, Y.; Choi, W. M.; Jiang, H.; Huang, Y.; Rogers, J. A. Nat. Nanotechnol. 2006, 1, 201.

(16) Takei, K.; Takahashi, T.; Ho, J. C.; Ko, H.; Gillies, A. G.; Leu, P. W.; Fearing, R. S.; Javey, A. *Nat. Mater.* **2010**, *9*, 821–826.

(17) Fan, Z.; Ho, J. C.; Jacobson, Z. A.; Yerushalmi, R.; Alley, R. L.; Razavi, H.; Javey *Nano Lett.* **2008**, *8*, 20–25.

(18) Friedman, R. S.; McAlpine, M. C.; Ricketts, D. S.; Ham, D.; Lieber, C. M. *Nature* **2005**, *434*, 1085.

(19) Cao, Q.; Kim, H. S.; Pimparkar, N.; Kulkarni, J. P.; Wang, C.; Shim, M.; Roy, K.; Alam, M. A.; Rogers, J. A. *Nature* **2008**, 454, 495–500.

(20) Sun, D. M.; Timmermans, M. Y.; Tian, Y.; Nasibulin, A. G.; Kauppinen, E. I.; Kishimoto, S.; Mizutani, T.; Ohno, Y. *Nat. Nanotechnol.* **2011**, *6*, 156–161.

(21) Avouris, P.; Chen, Z.; Perebeinos, V. Nat Nanotechnol. 2007, 2, 605-615.

(22) McEuen, P. L.; Fuhrer, M.; Park, H. *IEEE Trans. Nanotechnol.* 2002, 1, 78.

(23) Javey, A. ACS Nano 2008, 2, 1329-1335.

(24) Patil, N.; Lin, A.; Myers, E. R.; Ryu, K.; Badmaev, A.; Zhou, C.; Wong, H.-S. P.; Mitra, S. *Nano Lett.* **2009**, *8*, 498–504.

(25) Arnold, M. S.; Green, A. A.; Hulvat, J. F.; Stupp, S. I.; Hersam, M. C. Nat. Nanotechnol. 2006, 1, 60–65.

(26) Arnold, M. S.; Stupp, S. I.; Hersam, M. C. Nano Lett. 2005, 5, 713–718.

(27) Engel, M.; Small, J. P.; Steiner, M.; Freitag, M.; Green, A. A.; Hersam, M. C.; Avouris, P. ACS Nano **2008**, *2*, 2445–2452.

(28) Wang, C.; Zhang, J.; Ryu, K.; Badmaev, A.; Arco, L. G. D.; Zhou, C. Nano Lett. **2009**, *9*, 4285.

(29) Wang, C.; Zhang, J.; Zhou, C. ACS Nano 2010, 4, 7123-7132.

(30) Rouhi, N.; Jain, D.; Zand, K.; Burke, P. J. Adv. Mater. 2011, 23, 94–99.

(31) Kim, D. H.; Lu, N.; Ma, R.; Kim, Y. S.; Kim, R. H.; Wang, S.; Wu, J.; Won, S. M.; Tao, H.; Islam, A.; Yu, K. J.; Kim, T. I.; Chowdhury, R.; Ying, M.; Xu, L.; Li, M.; Chung, H. J.; Keum, H.; McCormick, M.; Liu, P.; Zhang, Y. W.; Omenetto, F. G.; Huang, Y.; Coleman, T.; Rogers, J. A. *Science* **2011**, 333, 838–843.

(32) Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. Nature 2003, 424, 654–657.

(33) Cao, Q.; Xia, M.; Kocabas, C.; Shim, M.; Rogers, J. A.; Rotkin, S. V. Appl. Phys. Lett. 2007, 90, 023516.

(34) Rosenblatt, S.; Yaish, Y.; Park, J.; Gore, J.; Sazonova, V.; McEuen, P. L. *Nano Lett.* **2002**, *2*, 869–872. (35) Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; McIntyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. *Nat. Mater.* **2002**, *1*, 241–246.

(36) Klauk, H. Organic Electronics: Materials, Manufacturing and Applications; Wiley-VCH: New York, 2006.

- (37) Kim, D. H.; Rogers, J. A. Adv. Mater. 2008, 20, 4887–4892.

- (38) Rogers, J. A.; Someya, T.; Huang, Y. Science 2010, 327, 1603–1607.

# **Supporting Information**

# **Carbon Nanotube Active Matrix Backplanes for Conformal Electronics**

Toshitake Takahashi<sup>1,2,3</sup>, Kuniharu Takei<sup>1,2,3</sup>, Andrew G. Gillies<sup>4</sup>, Ronald S. Fearing<sup>1</sup> and Ali Javey<sup>1,2,3</sup>

<sup>1</sup> Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94702

- <sup>2</sup> Berkeley Sensor and Actuator Center, University of California, Berkeley, CA 94720

- <sup>3</sup> Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

<sup>4</sup> Mechanical Engineering, University of California, Berkeley, CA 94702

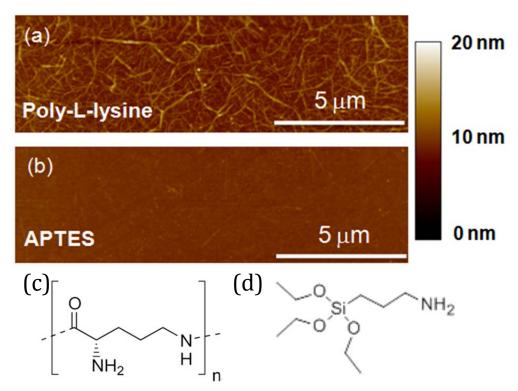

## SWNT-network density as a function of surface treatment

99% semiconductor enriched SWNTs are deposited on two different substrates. One is SiO<sub>2</sub>/Si substrate whose surface is oxygen plasma (30W for 1min) treated, followed by poly-L-lysine treatment for 5 min. The other is SiO<sub>2</sub>/Si substrate whose surface is oxygen plasma (30W for 1min) treated, followed by APTES treatment for 30min. The particular SWNTs used here (as-received, IsoNanotubes-S from NanoIntegris, Inc) adhere readily to the poly-L-lysine treated substrate.

**Figure S1. The effect of surface treatment on the deposited nanotube density.** The surface is treated with (**a**) poly-L-lysine for 5min and (**b**) aminopropyltriethyoxy silane (APTES) for 30min. SWNT deposition time is 20min. Chemical structure of (**c**) poly-L-lysine and (**d**) APTES.

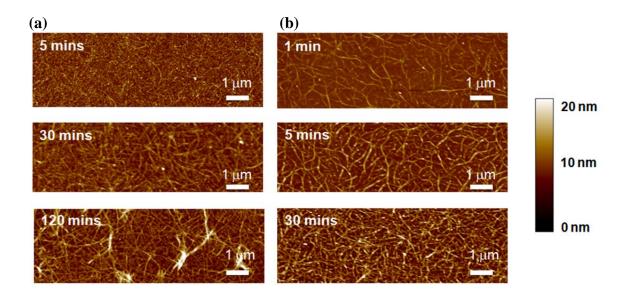

# SWNT-network density and bundling as a function of deposition time

**Figure S2.** AFM images taken from different SWNT deposition time on (**a**) evaporated  $SiO_2$  and (**b**) thermally grown  $SiO_2$ . For (**a**), 5min, 30 min, and 120 min are used, and for (**b**) 1 min, 5 min, and 30min are used as SWNT deposition time. The density increases as the deposition time increases, and eventually it forms nanotube bundles, degrading the device  $I_{ON}/I_{OFF}$  ratio.

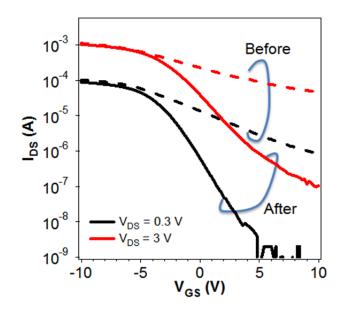

## The effect of vacuum annealing on the electrical properties of SWNT-TFTs

Transfer characteristics at  $V_{DS} = 0.3$  V and 3 V before and after vacuum annealing are shown in Fig. S2a. After vacuum annealing at 200 °C for 1h, both transconductance and  $I_{ON}/I_{OFF}$  ratio are dramatically improved. This improvement might possibly be due to the evaporation of surfactant residues.

**Figure S3. The effect of vacuum annealing on the device properties.** Transfer characteristics of a representative SWNT-network TFT before and after vacuum annealing at 200 °C for 1h.

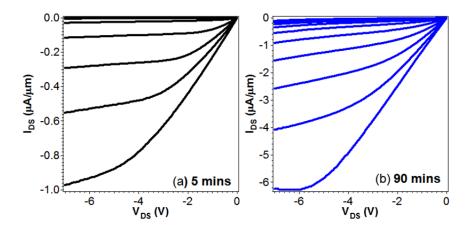

**Output characteristics of SWNT-TFTs**

Figure S4. Output characteristics of flexible SWNT-TFTs with two different SWNT densities. CNT deposition time of (a) 5 min and (b) 90 min. Applied  $V_g$  is from -10 V to 0 V with 1 V step from bottom to top.

## Stretchable honeycomb structures

By changing the side length of the hexagonal holes with a fixed period of 3.3 mm, the stretching properties are tuned. Here, the x-component of stress tensor when the substrate is stretched by 2 mm is mechanically simulated with COMSOL for four different side lengths of hexagonal holes (from 1 mm to 1.85 mm). Clearly, the induced stress is reduced as the hole size increases, which is consistent with stretchability results in Fig. 3a. The active devices are placed as marked in blue circle in Fig. S6 c, where induced stress is minimum. This supports the experimental results in Fig. 4c.

Figure S5. Mechanical simulation results for honeycomb patterned PI substrates with a side length of the hexagon holes being (a) a = 1.85 mm, (b) a = 1.5 mm, (c) a = 1.25 mm, (d) a = 1 mm. Here, the substrate is stretched by 2 mm in the x-direction.