### NANO LETTERS

2009 Vol. 9, No. 2 725-730

# Wafer-Scale, Sub-5 nm Junction Formation by Monolayer Doping and Conventional Spike Annealing

Johnny C. Ho,<sup>†,‡,§</sup> Roie Yerushalmi,<sup>†,‡,§,+</sup> Gregory Smith,<sup>||</sup> Prashant Majhi,<sup>||</sup> Joseph Bennett,<sup>⊥</sup> Jeffri Halim,<sup>¶</sup> Vladimir N. Faifer,<sup>¶</sup> and Ali Javey\*,<sup>†,‡,§</sup>

Department of Electrical Engineering and Computer Sciences, Berkeley Sensor and Actuator Center, University of California at Berkeley, Berkeley, California 94720, Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, SEMATECH, Austin, Texas 78741, SVTC Technologies, Austin, Texas 78741, and Frontier Semiconductor, Inc., San Jose, California 95112

Received October 28, 2008; Revised Manuscript Received December 11, 2008

#### **ABSTRACT**

We report the formation of sub-5 nm ultrashallow junctions in 4 in. Si wafers enabled by the molecular monolayer doping of phosphorus and boron atoms and the use of conventional spike annealing. The junctions are characterized by secondary ion mass spectrometry and noncontact sheet resistance measurements. It is found that the majority ( $\sim$ 70%) of the incorporated dopants are electrically active, therefore enabling a low sheet resistance for a given dopant areal dose. The wafer-scale uniformity is investigated and found to be limited by the temperature homogeneity of the spike anneal tool used in the experiments. Notably, minimal junction leakage currents (<1  $\mu$ A/cm²) are observed that highlights the quality of the junctions formed by this process. The results clearly demonstrate the versatility and potency of the monolayer doping approach for enabling controlled, molecular-scale ultrashallow junction formation without introducing defects in the semiconductor.

Device scaling has been the main driving force for the technology advancement in the semiconductor industry over the last few decades.<sup>1,2</sup> Specifically, junction depths have been scaled continuously together with the gate lengths in order to achieve faster transistor speeds and higher packing densities. Historically, source/drain extension junction depths of  $\sim 1/3$  of the transistor gate lengths have been used for efficient electrostatics and acceptable leakage currents. With the gate lengths fast approaching the sub-10 nm regimes, it is vital to realize sub-5 nm ultrashallow junctions (USJs) with low sheet resistivity (i.e., low parasitic contact resistance) to facilitate the future scaling of transistors. However, there are tremendous technological challenges for achieving sub-5 nm USJs as the conventional doping strategies suffer from a number of setbacks. 1,2 The current USJs are fabricated by the combination of ion implantation and spike annealing. During the process, Si atoms are displaced by energetic dopant ions and a subsequent annealing step (e.g., spike, a high temperature anneal process of less than 1 s with fast temperature ramp up/down capability) is used to activate the dopants by moving them into the appropriate lattice positions and restoring the substrate's crystal quality. However, point defects such as Si interstitials and vacancies are also generated, which interact with the dopants to further broaden the junction profile. This is known as the transient-enhanced diffusion (TED),<sup>3</sup> which limits the formation of sub-10 nm USJs by conventional technologies. Moreover, there are significant research efforts to develop new strategies such as utilizing heavier implantation dopant sources (molecular implantation,<sup>4</sup> gas cluster ion beam<sup>5</sup> and plasma doping<sup>6</sup>) to obtain shallower doping profiles, and advanced annealing techniques (flash<sup>7</sup> and laser<sup>8</sup>) to activate the implanted dopants without causing significant diffusion. However, very little is known on the effects of advanced doping and annealing techniques on the junction uniformity, reliability, and subsequent process integration that may hamper their use in the IC manufacturing. To address the need for advanced doping strategies, recently we reported a new technique for controlled, nanoscale surface doping of semiconductor materials by utilizing the crystalline nature of silicon and its self-limiting surface reaction properties to form

<sup>\*</sup> To whom correspondence should be addressed. E-mail: ajavey@eecs.berkeley.edu.

$<sup>^\</sup>dagger$  Department of Electrical Engineering and Computer Sciences, University of California at Berkeley.

<sup>&</sup>lt;sup>‡</sup> Lawrence Berkeley National Laboratory.

<sup>§</sup> Berkeley Sensor and Actuator Center, University of California at Berkeley.

<sup>&</sup>quot;SEMATECH.

<sup>&</sup>lt;sup>⊥</sup> SVTC Technologies.

<sup>¶</sup> Frontier Semiconductor, Inc.

<sup>&</sup>lt;sup>+</sup> Current address: Institute of Chemistry, The Hebrew University of Jerusalem.

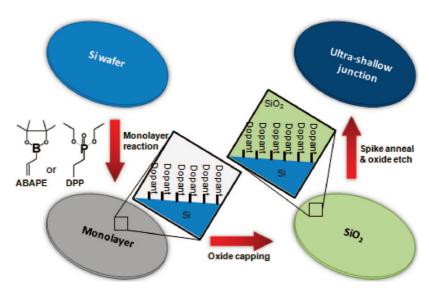

Figure 1. Process schematic for the wafer-scale monolayer doping approach.

self-assembled dopant monolayers followed by a subsequent annealing step for the incorporation and diffusion of dopants. Because of the lack of damage to the lattice during this surface-doping strategy, minimal TED effects are expected which presents a major advantage of this technology for achieving nanoscale junctions. Previously, we reported junction depths down to  $\sim 20$  nm by utilizing the monolayer doping method and 5 s rapid thermal diffusion. Here, we explore and characterize the junction depth limits of this process on wafer-scale and in detail through materials and electrical characterizations. Uniquely, for the first time, we demonstrate sub-5 nm junction depths (down to  $\sim 2$  nm, which is at the limit of most characterization methods) with low sheet resistivity, even for fast diffusing dopants such as phosphorus.

The monolayer doping (MLD) process is based on the formation of self-assembled dopant-containing monolayer on the crystalline silicon surfaces, followed by the subsequent diffusion of dopants from the surface into the lattice by a thermal annealing step (Figure 1). In detail, for the phosphorus-MLD (P-MLD) process, 4 in. p-type Si wafers were first treated with dilute hydrofluoric acid (~1%) to remove the native SiO<sub>2</sub>. The Si surface was then reacted with diethyl 1-propylphosphonate (DPP, Alfa Aesar) and mesitylene as a solvent (25:1, v/v) for 2.5 h at 120 °C to assemble a P-containing monolayer. The details of this reaction and the monolayer formation kinetics have been reported elsewhere.  $^{9,10}$  Then, a layer of  $\sim 50$  nm thick SiO<sub>2</sub> is electronbeam evaporated as a cap, and the substrate is spike annealed between 900-1050 °C in Ar ambient to drive in the P atoms and achieve n<sup>+</sup>/p USJs. The spike annealing is performed in a rapid thermal processing tool (AG Associate, model 610) with a fast ramping rate of 100 °C/s to the target temperature. During the annealing, the 4 in. Si wafer is placed on top of a 6 in. pocket wafer and temperature is monitored by the pyrometer controlling system. A similar approach was applied to 4 in. n-type Si wafers for boron-MLD (B-MLD) for which hydrogen-terminated Si wafers were reacted with allylboronic acid pinacol ester (ABAPE, Aldrich) and mesitylene as a solvent (25:1, v/v) at 120 °C for 2.5 h to enable a B-containing monolayer that is then capped with  $SiO_2$  followed by spike anneal to enable the formation of  $p^+/n$  USJs. Finally, the oxide cap is removed and the enabled junctions are characterized.

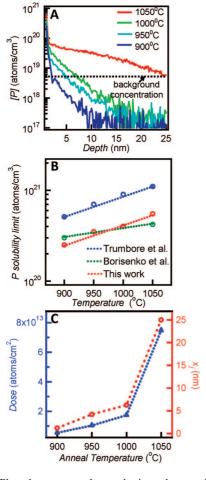

Secondary ion mass spectrometry (SIMS) measurements were performed to characterize the dopant profiles. Figure 2A illustrates the phosphorus SIMS profiling for P-MLD with spike anneal temperatures of 950-1050 °C. Notably, for all samples there is a dramatic change in the P profile at the concentration of  $1 \sim 5 \times 10^{19}$  atoms/cm<sup>3</sup>, which is known as the "kink-and-tail" characteristic. This behavior has been commonly observed for the conventional phosphorus doping schemes<sup>11</sup> and is attributed to the changeover from the vacancy-assisted diffusion mechanism (at high P concentration region) to the kick-out diffusion mechanism (at low P concentration region).<sup>12</sup> From the temperature dependency, two trends are clearly evident. First, the surface concentration of incorporated P monotonically increases with the annealing temperature (Figure 2B). Specifically, surface doping concentrations of  $N_0 \sim 2.5 \times 10^{20}$ ,  $3.5 \times 10^{20}$ ,  $4 \times 10^{20}$ ,  $5.5 \times 10^{20}$  $10^{20}$  atoms/cm<sup>3</sup> are observed for 900, 950, 1000, 1050 °C, respectively. This trend is consistent with the constant source, surface diffusion model, in which  $N_0$  is governed by the dopant solubility limit at the diffusion temperature. In fact, the observed temperature dependency of  $N_0$  is in close agreement with the previously reported solid solubility limits (Figure 2B). 13,14 In the MLD process, the maximum areal dose, Q, corresponds to the monolayer packing density ( $\sim$ 8 × 10<sup>14</sup> molecules/cm<sup>2</sup> assuming a molecular footprint of  $\sim 0.12 \text{ nm}^2$ ); hence, at a first glance, it may seem that the limited source diffusion model is more applicable. However, in this work, since spike annealing is applied, the monolayer packing density is higher than the areal dose of the incorporated/diffused dopants. Therefore, within the context of this work, constant source model may be applied as a rough guideline in predicting the doping profile behaviors.

The second clear trend observed from the SIMS profiling is a monotonic increase in the junction depth and areal dopant

**Figure 2.** Phosphorus monolayer doping characterization. (A) Secondary ion mass spectrometry (SIMS) profile of phosphorus atoms for different spike anneal temperatures. (B) Phosphorus surface concentration,  $N_0$  obtained from SIMS analysis for MLD-processed samples as a function of spike annealing temperature. For comparison, the previously reported solid—solubility limits for different temperatures are also shown. (C) Phosphorus areal dose vs junction depth (at a background of  $5 \times 10^{18}$  atoms/cm³) for different spike anneal temperatures.

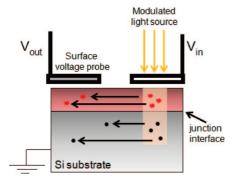

**Figure 3.** Noncontact  $R_s$  and junction leakage current measurement schematic.

dose with the diffusion temperature. The junction depth,  $x_j$  is defined as the depth at which the incorporated P concentration equates the background B concentration of the substrate ( $\sim 5 \times 10^{18}$  B atoms/cm<sup>3</sup>), while Q is extracted by integrating the total area of the dopant profiles. Notably, the substrate concentration of  $5 \times 10^{18}$  atoms/cm<sup>3</sup> used here is the same as the channel doping density for the state-of-the

art Si MOSFETs. We extract  $x_j \sim 2$ , 5, 7, 25 nm and  $Q \sim 5.5 \times 10^{12}$ ,  $1.0 \times 10^{13}$ ,  $1.7 \times 10^{13}$ ,  $7.5 \times 10^{13}$  P atoms/cm² for 900, 950, 1000, 1050 °C spike anneals, respectively (Figure 2C). This trend is expected and arises from the enhanced diffusivity and solubility of P in Si at higher diffusion temperatures. It should be noted that given the finite temperature ramp time ( $\sim 100$  °C/s) of our rapid thermal annealing tool, the diffusion time is also effectively increased for the samples treated at higher annealing temperatures, which may also attribute to the observed temperature dependency of the dopant dose.

The sub-5 nm USJs with high Q enabled by MLD are highly attractive and clearly demonstrate the potency and viability of this technology for future nanoscale complementary metal oxide semiconductor (CMOS) fabrication processing. This unique feature of MLD arises from the lack of TED during the dopant incorporation, which is in distinct contrast to the ion implantation process. Additionally, in the MLD process the incorporated dopant atoms near the surface are not lost during the SiO<sub>2</sub> cap (i.e., mask) removal step, owing to the high etch selectivity of the oxide over crystalline Si. This is in distinct contrast to the ion implantation process in which the post-implantation mask removal and surface cleaning steps lead to some dopant (and Si) loss near the surface due to the enhanced etch rate and reduced etch selectivity of the damaged (nearly amorphized by the implanted ions) top Si layer. Uniquely, this work shows that conventional annealing methods can indeed enable sub-5 nm USJs when dopants are introduced from the surface, which is yet another beneficial aspect of MLD since the uniformity and reliability of sub-millisecond, nonequilibrium annealing methods<sup>7,8</sup> (i.e., flash and laser) are still unknown and under active investigation.

While SIMS is highly valuable for obtaining the overall dopant profiles, some uncertainty and error may be expected in the measured profiles, especially for the first 1-2 nm depth from the surface and even when the measurement tool is cautiously operated near the depth resolution limit (see Supporting Information). Additionally, SIMS does not provide information on the electrically active content of the incorporated dopants, which is critical for the device applications. Therefore, to further characterize the n<sup>+</sup>/p USJs and examine the electrically active concentration of the incorporated dopants, sheet resistance  $(R_s)$  measurements are imperative. However, accurate  $R_s$  measurements are quite challenging for USJs. Specifically, conventional contactmode, four-point probe measurements cannot be utilized for sub-10 nm USJs because of the probe penetration into the surface of the substrate.<sup>15</sup> This probe penetration causes significant junction damage and leakage which underestimates the true  $R_s$  with a corresponding error as high as 100% or more. 15 In this aspect, we utilized the noncontact  $R_s$ technique to electrically characterize our USJs. Briefly, this method relies on the principle of measuring the difference in the surface photovoltage between two noncontact, voltage probes as induced by an external light source (Figure 3). By varying the light modulation frequency, the spatially resolved surface voltage can yield an accurate estimation of  $R_s$  and

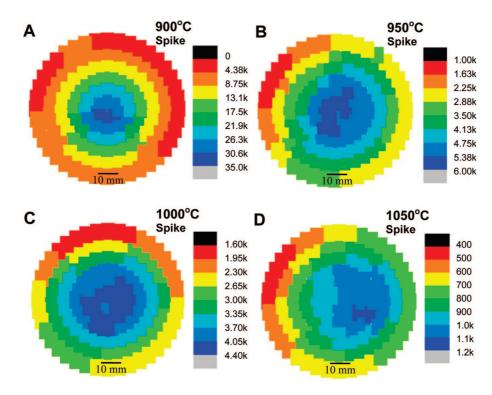

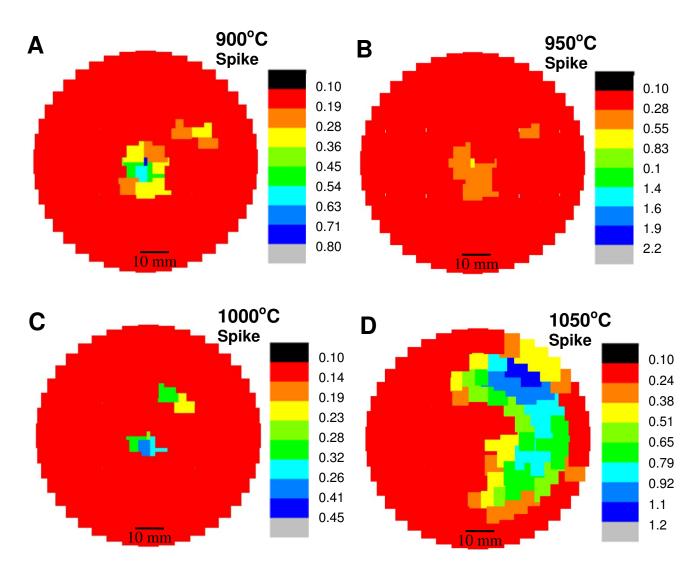

Figure 4. Noncontact sheet resistance (in  $\Omega/\square$ ) wafer map for P-MLD samples with spike anneal temperatures of (A) 900, (B) 950, (C) 1000, and (D) 1050 °C.

**Figure 5.** (A) Sheet resistance (in  $\Omega/\square$ ) versus  $x_j$  for phosphorusdoped Si samples reported in this work (by P-MLD) and the literature (by conventional doping methods). The dot line shows a simple constant source diffusion model (see Supporting Information) for comparison purposes. (B) Dopant activation efficiency for P-MLD samples as a function of spike annealing temperature.

the junction leakage current density with the details reported elsewhere. <sup>16</sup> Figure 4 shows the noncontact  $R_s$  wafer maps for the n<sup>+</sup>/p junctions enabled by MLD. Average  $R_s \sim 12\,000,\,3670,\,3160,\,825\,\Omega/\square$  are observed for the 900, 950, 1000 and 1050 °C spike anneals, respectively. This temperature dependency is expected due to the higher diffusivity and solubility of dopants (i.e., higher Q) at higher temper-

atures, which effectively results in higher free carrier concentrations and lower  $R_s$ .

From the wafer-scale  $R_s$  maps, a modest standard deviation of  $\sigma \leq 30\%$  is obtained for all samples, except for the 900  $^{\circ}$ C spike annealed wafer (Figure 4). The large variation ( $\sigma$  $\sim 100\%$ ) in the  $R_s$  for the 900 °C spike wafer may be due to the average measured  $R_{\rm s} \sim 12~00~\Omega/\Box$  being close to the resolution limit of the noncontact  $R_s$  measurement set up. Notably, clear rotational symmetry is observed in the  $R_s$  maps for all samples with  $R_s$  being highly uniform ( $\sigma < 5\%$ ) within each circular "ring" boundaries. This variation pattern is a signature of the spatial imbalance in the power density of the heater lamp, <sup>17</sup> which may be expected since the annealing tool used in this study was not designed for spike anneal applications.<sup>18</sup> Notably, the ring pattern is off-centered for the 1050 °C wafer (Figure 4D) because the wafer was misaligned from the center of the support substrate during the annealing step, again indicative of the role of the nonuniform heating in the observed  $R_s$  variation. Given that  $R_{\rm s}$  is highly uniform within each ring, we speculate that in the future, a higher uniformity across the wafer may be attained by MLD if a more sophisticated spike annealing tool is used. This is an expected feature of MLD since the dopants are deterministically positioned on the surface of the wafer through a self-limiting monolayer formation reaction, therefore, providing a high degree of control in the uniformity of surface dopant coverage prior to the diffusion step.

In order to compare our P-MLD processed n<sup>+</sup>/p USJs with those achieved by other doping technologies, we complied the literature reported  $R_s$  and  $x_j$  values for phosphorus doped junctions as depicted in Figure 5A. <sup>19–23</sup> From the literature,

the smallest  $x_j \sim 13$  nm at the background concentration of  $5 \times 10^{18}$  atoms/cm<sup>3</sup> was reported with  $R_s \sim 650$   $\Omega$ /cm. To the best of our knowledge, there is no previous report of sub-10 nm n<sup>+</sup>/p USJs based on the phosphorus diffusion in part because of the high diffusivity of P, highlighting the elegance of MLD in achieving nanometer-scale junctions, even for fast diffusing impurities. Notably, for  $x_j \sim 25$  nm, the  $R_s$  values obtained from MLD are comparable (within a factor of  $\sim$ 2) with those obtained by other conventional doping methods (Figure 5A). Moreover, a simple, analytical constant-source diffusion modeling (P in Si) was carried out (Figure 5A) to further shed light on the MLD experimental data (see Supporting Information for details). The experimental values qualitatively fit the modeling trend, again demonstrating the near ideal behavior of the MLD process.

From the SIMS and  $R_{\rm s}$  measurements, the phosphorus activation efficiency,  $\eta$ , was directly obtained for each diffusion temperature (Figure 5B) in order to shed light on the percentage of the incorporated dopants that are electrically active. Specifically,  $R_{\rm s}$  was estimated from the SIMS profiles by eq 1 and then compared to the noncontact  $R_{\rm s}$  measurement values

$$R_{\text{s,SIMS}}^{-1} = \int_{0}^{x_{\text{j}}} q\mu(N)N(x)dx \tag{1}$$

where q,  $\mu$ , N, and x are the elemental charge, electron mobility, dopant concentration, and depth, respectively. The efficiency is then defined as  $\eta = (R_{s,SIMS})/(R_{s,measurement})$ . Figure 5B shows the extracted efficiencies of  $\eta \sim 70\%$  for spike annealing temperatures  $\geq 950$  °C with  $\eta \sim 30\%$  for the 900 °C spike anneal. The discrepancy between the measured and calculated  $R_s$  values may be attributed to some percentage of the diffused dopants that are incorporated in sites other than substitutional lattice sites. 12 However, since in the MLD dopants are introduced from the surface by an equilibrium process, we expect the diffusion of dopants to be dominated by the substitutional mechanism, resulting in nearly all the incorporated dopants being electrically active. Therefore, we speculate that the small discrepancy between the measured and calculated  $R_s$  values arise from the uncertainty in the SIMS profiles. This error is particularly magnified for the 900 °C wafer since the observed junction depth is only  $\sim$ 2 nm for this sample, right at the resolution limit of SIMS. The high  $\eta$  estimated from the data analysis is yet another highly attractive feature of MLD since for device applications, only the electrically active contents are desirable with other dopants inducing defects and/or junction leakage currents.

Since organic molecular precursors are utilized as the dopant source, carbon incorporation during the dopant diffusion may be expected, which may enhance the highly undesired junction leakage currents. Therefore, investigations of C incorporation and the arising junction properties are needed. However, SIMS measurements do not provide accurate C depth profiling near the surface region due to the atmospheric organic surface contaminants that is unavoidable even if a premeasurement cleaning step is performed on the samples.<sup>24</sup> Instead, in order to directly characterize the effect of potential carbon incorporation, the junction leakage current density was measured by the noncontact, photovoltage

measurement. Figure S3 in Supporting Information illustrates the leakage current wafer map for the  $\rm n^+/p$  junctions for various spike temperatures. The average leakage currents of  $\sim\!0.13,\,0.55,\,0.11,\,0.31\,\mu\rm A/cm^2$  were measured for the 900, 950, 1000, 1050 °C spike anneals, respectively. Notably, the small leakage currents (<1  $\mu\rm A/cm^2$ ) are close to the resolution limit of the instrument and attest to the high quality junctions that are enabled by MLD. The results suggest that carbon content incorporation may not be of a concern for MLD, at least when considering the junction leakage currents, which are smaller than the state-of-the-art USJs' leakage currents.  $^{25}$

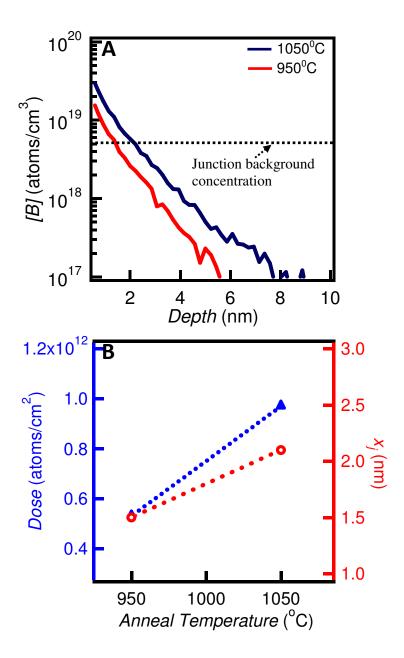

In addition to the  $n^+/p$  junctions, we also investigated the formation of p<sup>+</sup>/n USJs by boron-MLD with spike annealing. From SIMS measurements, sub-2 nm junction depths ( $x_i \sim$ 1 and 2 nm) are obtained for 950 and 1050 °C spike, respectively (Figure S1 in Supporting Information), which is close to the resolution limit of SIMS. The more shallow junctions enabled at the same diffusion temperature for B-MLD as compared to P-MLD is expected due to the lower diffusivity of B. Since the B-MLD p<sup>+</sup>/n junctions are at the molecular-scale, the  $R_{\rm s}$  values were higher than  $\sim 10~000~\Omega/\Box$ for all spike conditions and therefore out of the measurement range of the noncontact photovoltage characterization technique. In the future, more advanced electrical and materials characterization methods, such as local electrode atom probe microscopy, need to be utilized to further study the amazingly shallow p<sup>+</sup>/n USJs enabled by MLD.

In summary, we have demonstrated the wafer-scale formation of n<sup>+</sup>/p and p<sup>+</sup>/n USJs by the combination of selflimiting monolayer doping and the conventional spike annealing. This approach is demonstrated on 4 in. Si wafers with the junction uniformity limited by the temperature homogeneity of the spike anneal tool. For phosphorus doping, we report for the first time, sub-10 nm junction formation (down to 2 nm - the SIMS resolution limit) with the noncontact  $R_s$  measurements being consistent with the predicted values from the dopant profiles. Additionally, we find minimal junction leakage currents that are indicative of high quality, defect-free USJs enabled by MLD. Notably, besides nanoscale controlled doping for the contact extension of future MOSFETs, this surface-doping technology also may be highly applicable for the conformal and deterministic doping of nonplanar nanoscale device structures, such as Fin-FETs or nanowire-FETs.

**Acknowledgment.** This work was financially supported by SEMATECH, NSF, Intel Corporation, and MARCO MSD Focus Center Research Program. J.C.H acknowledges a graduate student fellowship from Intel Foundation. R.Y. acknowledges a Human Frontiers Science Program fellowship.

**Supporting Information Available:** Details of SIMS measurements; activation efficiency ( $\eta$ ) calculations; constant source diffusion modeling; and noncontact junction leakage measurements. This material is available free of charge via the Internet at http://pubs.acs.org.

#### References

- Peercy, P. S. The drive to miniaturization. *Nature* 2000, 406, 1023– 1026.

- (2) Claeys, C. Technological challenges of advanced CMOS processing and their impact on design aspects. 17th International Conference Proceedings on VLSI Design 2004, 2004, 275–282.

- (3) Stolk, P. A.; Gossmann, H. J.; Eaglesham, D. J.; Poate, J. M. Implantation and transient boron diffusion: the role of Si self interstitials. *Nucl. Instrum. Methods Phys. Res.*, Sect. B 1995, 96, 187.

- (4) Kawasaki, Y.; Kuroi, T.; Yamashita, T.; Horita, K.; Hayashi, T.; Ishibashi, M.; Togawa, M.; Ohno, Y.; Yoneda, M.; Horshy, T.; Jacobson, D.; Krull, W. Ultra-shallow junction formation by B<sub>18</sub>H<sub>22</sub> ion implantation. *Nucl. Instrum. Methods Phys. Res., Sect. B* 2005, 237, 25–29.

- (5) MacCrimmon, R.; Hautala, J.; Gwinn, M.; Sherman, S. Gas cluster ion beam infusion processing of semiconductors. *Nucl. Instrum. Methods Phys. Res., Sect. B* 2006, 242, 427–30.

- (6) Yon, G. H.; Buh, G. H.; Park, T.; Hong, S. J.; Shin, Y. G.; Chung, U.; Moon, J. T. Ultra Shallow Junction Formation Using Plasma Doping and Laser Annealing for Sub-65 nm Technology Nodes. *Jpn. J. Appl. Phys.* 2006, 45, 2961–2964.

- (7) Ito, T.; Iinuma, T.; Murakoshi, A.; Akutsu, H.; Suguro, K.; Arikado, T.; Okumura, K.; Yoshioka, M.; Owada, T.; Imaoka, Y.; Murayama, H.; Kusuda, T. 10–15 nm Ultrashallow Junction Formation by Flash-Lamp Annealing. *Jpn. J. Appl. Phys.* 2002, 41, 2394–98.

- (8) Poon, C. H.; Cho, B. J.; Lu, Y. F.; Bhat, M.; See, A. Multiple-pulse laser annealing of preamorphized silicon for ultrashallow boron junction formation. J. Vac. Sci. Technol., B 2003, 21 (2), 706–709.

- (9) Ho, J. C.; Yerushalmi, R.; Jacobson, Z. A.; Fan, Z.; Alley, R. L.; Javey, A. Controlled nanoscale doping of semiconductors via molecular monolayers. *Nat. Mater.* 2008, 7 (1), 62–67.

- (10) Yerushalmi, R.; Ho, J. C.; Fan, Z.; Javey, A. Phosphine Oxide Monolayers on SiO<sub>2</sub> Surfaces. Angew. Chem., Int. Ed. 2008, 47, 4440– 4442

- (11) Bentzen, A.; Schubert, G.; Christensen, J. S.; Svensson, B. G.; Holt, A. Influence of temperature during phosphorus emitter diffusion from a spray-on source in multicrystalline silicon solar cell processing. *Prog. Photovoltaics* 2007, 15, 281–289.

- (12) Uematsu, M. Simulation of boron, phosphorus, and arsenic diffusion in silicon based on an integrated diffusion model, and the anomalous phosphorus diffusion mechanism. J. Appl. Phys. 1997, 82–5, 2229.

- (13) Trumbore, F. A. Solid Solubilities of Impurity elements in Ge and Si. *Bell Syst. Tech. J.* **1960**, *35*, 205.

- (14) Borisenko, V. E.; Yudin, S. G. Steady-State Solubilities of Subsitutional Impurities in Si. Phys. Status Solidi A 1987, 1 (101), 123–127.

- (15) Clarysse, T.; Vanhaeren, D.; Vandervorst, W. Impact of probe penetration on the electrical characterization of sub-50 nm profiles. J. Vac. Sci. Technol., B 2002, 20 (1), 459–66.

- (16) Faifer, V. N.; Current, M. I.; Wong, T. M. H.; Souchkov, V. V. Noncontact sheet resistance and leakage current mapping for ultra-shallow junctions. J. Vac. Sci. Technol., B. 2008, 26 (1), 420–24.

- (17) Faifer, V. N.; Current, M. L.; Nguyen, T.; Wong, T. M. H.; Souchkov, V. V. Non-contact measurement of sheet resistance and leakage current: applications for USJ-SDE/halo junctions. *Ext. Abs. of the 5th IWJT, IEEE* 2005, pp 45–8.

- (18) Since the 4 in. wafer is placed on a support substrate during the spike annealing (the tool was designed to handle 6 in. wafers), this may also contribute to the variation pattern.

- (19) Collarta, E. J. H.; Felch, S. B.; Pawlak, B. J.; Absil, P. P.; Severi, S.; Janssens, T.; Vandervorst, W. Co-implantation with conventional spike anneal solutions for 45 nm *n*-type metal-oxide-semiconductor ultrashallow junction formation. *J. Vac. Sci. Technol., B.* 2006, 24 (1), 507–9

- (20) Augendre, E.; Pawlak, B. J.; Kubicek, S.; Hoffmann, T.; Chiarella, T.; Kerner, C.; Severi, S.; Falepin, A.; Ramos, J.; De Keersgieter, A.; Eyben, P.; Vanhaeren, D.; Vandervorst, W.; Jurczak, M.; Absil, P.; Biesemans, S. Superior N- and P-MOSFET scalability using carbon co-implantation and spike annealing. *Solid-State Electron.* 2007, 51 (11–12), 1432–6.

- (21) Lee, S. W.; Jeong, J. Y.; Park, C. S.; Kim, J. H.; Ji, J. Y.; Choi, J. Y.; Lee, Y. J.; Han, S. H.; Kim, K. M.; LeeW. J.; Rha, S. K.; Oh, J. K. The study of plasma doping process for ultra shallow junctions. *Ext. Abs. of the 7th IWJT, IEEE* **2007**, 67–8.

- (22) Cagnat, N.; Laviron, C.; Mathiot, D.; Rando, C.; Juhel, M. Shallow Junction Engineering by Phosphorus and Carbon Co-implantation: Optimization of Carbon Dose and Energy. *Mater. Res. Soc. Symp. Proc.* 2007, 994, 0994-F08-04.

- (23) Pawlak, B. J.; Duffy, R.; Augendre, E.; Severi, S.; Janssens, T.; Absil, P.; Vandervorst, W.; Collart, E.; Felch, S.; Schreutelkamp, R.; Cowern, N. The Carbon Co-Implant with Spike RTA Solution for Phosphorus Extension. *Mater. Res. Soc. Symp. Proc.* 2006, 912, 0912-C01-06.

- (24) Beebe, M.; Bennett, J.; Barnett, J.; Berlin, A.; Yoshinaka, T. Quantifying residual and surface carbon using polyencapsulation SIMS. Appl. Surf. Sci. 2004, 231–32, 716–19.

- (25) Chen, J. T. C.; Dimitrova, T.; Dimitrov, D. A New Method for Mapping Ultra-Shallow Junction Leakage Currents. *International Workshop on IWJT, IEEE* 2006, 100.

NL8032526

## **Supporting Information**

# Wafer-Scale, Sub-5 nm Junction Formation by Monolayer Doping and Conventional Spike Annealing

Johnny C. Ho, <sup>1,2,3</sup> Roie Yerushalmi, <sup>1,2,3,†</sup> Gregory Smith, <sup>4</sup> Prashant Majhi, <sup>4</sup> Joseph Bennett, <sup>5</sup> Jeffri Halim, <sup>6</sup> Vladimir N. Faifer, <sup>6</sup>Ali Javey <sup>1,2,3,\*</sup>

<sup>1</sup>Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA, 94720, USA.

<sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720, USA.

<sup>3</sup>Berkeley Sensor and Actuator Center, University of California at Berkeley, Berkeley, CA, 94720, USA.

<sup>4</sup>SEMATECH, Austin, TX, 78741, USA.

<sup>5</sup>SVTC Technologies, Austin, TX, 78741, USA.

<sup>6</sup>Frontier Semiconductor, Inc., San Jose, CA, 95112, USA.

† Current address: Institute of Chemistry, The Hebrew University of Jerusalem

\* Corresponding author: ajavey@eecs.berkeley.edu

#### **Details of SIMS measurements for P profiling**

The SIMS measurements reported for the n+/p USJs were performed on the front side of the samples after the oxide caps were removed in HF. The samples were then etched in standard clean solution (SC1, mixture of ammonia hydroxide / hydrogen peroxide / de-ionized water) to remove organic material before the analyses. The analyses were performed on the Physical Electronics ADEPT-1010. The P+<sup>30</sup>Si signal was monitored as negative ions under 500eV Cs<sup>+</sup> bombardment incident at 60°. Secondary ions were collected from the center 20% of a 400 µm x 400 µm rastered area. Stylus profilometry was used to determine the depth of the craters and calibrate the depth scale. The P concentration was calculated using a relative sensitivity factor (RSF) determined from a standard sample. Importantly, the SC1 clean effectively removed the organic contamination that was interfering with the P signal. We noted that the SCI clean oxidized the Si surface but would not affect the SIMS measurement. The profiles obtained after the cleaning give a much valid representation of the P distribution.

SIMS measurements for front-side depth profiling of P thru the oxide cap were also performed but the organic monolayer induces an additional sample charging just beyond the oxide/Si interface and this interference distorts the signals collected and makes the profiles invalid. Moreover, backside SIMS measurements were carried out as well; however, backside profiling requires the sample thinning down to 100nm in which imposes a huge technical challenge to obtain reliable profiles in USJs.

## **Boron MLD**

Figure S1. Boron monolayer doping characterization. A. Secondary Ion Mass Spectrometry (SIMS) profile of boron for different spike anneal temperatures. B. SIMS extracted boron dose versus junction depth (at a background of  $5x10^{18}$  atoms/cm<sup>3</sup>) for different spike anneal temperatures.

In addition to the n+/p junctions, we also investigate the formation of p+/n USJs by boron-MLD with spike annealing. Figure S1 shows the SIMS profiles of diffused boron atoms in the junctions for both 950 and  $1050^{\circ}$ C spike. The profiles decrease sharply from low  $10^{19}$  cm-3 on the surface to the junction. We extracted  $x_j$ ~1.5, 2.1 nm and Q~5.3x10<sup>11</sup>, 9.7x10<sup>11</sup> B aomts/cm<sup>2</sup> for 950, 1050°C spike anneals, respectively (Fig. S1B). This trend is expected and arises from the enhanced diffusivity and solubility of B in Si at higher diffusion temperatures. We note that the SIMS profiles and junction depths attained here are at the resolution limit of SIMS analysis which may create some uncertainties in the exact accuracy of the profiles.

The SIMS measurements here were done similar to the ones of n+/p USJs. Front-side depth profiling of B was performed after the oxide caps were removed in HF. The analyses were carried out in the Physical Electronics ADEPT-1010. The <sup>11</sup>B signal was monitored as a positive ion under 650eV O<sub>2</sub><sup>+</sup> bombardment incident at 45°. The analysis chamber was backfilled with a high partial pressure of O<sub>2</sub> to reduce ion yield variations at the beginning of the profile. Secondary ions were collected from the center 20% of a 400 µm x 400 µm rastered area. Stylus profilometry was used to determine the depth of the craters and calibrate the depth scale. The B concentration was calculated using a relative sensitivity factor (RSF) determined from a standard sample. Again, both front-side profiling thru the oxide cap and back-side profiling were also explored but same challenges came up similar to the ones of n+/p USJs.

#### Activation efficiency $(\eta)$ calculations

From SIMS profiles, assuming all the dopants are fully activated, the  $R_{s,SIMS}$  can be estimated by dividing the profile into many thin slabs. Each  $R_{s,slab}$  can be calculated as the Equation S1<sup>S1</sup>,

$$R_{s,slab} = \frac{\rho}{x} = \frac{1}{qN\mu x}$$

Eq. S1

$$R_{s,slab} = \frac{\rho}{x} = \frac{1}{qN\left[\mu_{\min} \frac{\mu_{\max} - \mu_{\min}}{(1 + \frac{N}{N_r})^{\alpha}}\right]} x$$

|                                          | Phosphorous           |

|------------------------------------------|-----------------------|

| $\mu_{min}$ (cm <sup>2</sup> /Vs)        | 68.5                  |

| $\mu_{\text{max}}$ (cm <sup>2</sup> /Vs) | 1414                  |

| N <sub>r</sub> (cm <sup>-3</sup> )       | 9.20x10 <sup>16</sup> |

| α                                        | 0.711                 |

where  $\rho$ , x, q, N and  $\mu$  are the resistivity, thickness, elemental charge, dopant concentration, carrier mobility of the slab, respectively. The  $R_{s,SIMS}$  can be found by summing all the resistance of the slabs,  $\frac{1}{R_{s,SIMS}} = \sum \frac{1}{R_{s,slab}}$ . This  $R_{s,SIMS}$  can then be compared to the measured  $R_s$  in order to determine the activation efficiency,  $\eta = \frac{R_{s,SIMS}}{R_{s,measurement}}$ .

For example,  $R_{s,SIMS}$  was determined to be ~600  $\Omega/\Box$  from the SIMS profile of the n+/p  $1050^{\circ}$ C spike anneal. Also,  $R_{s,measurement}$  was found to be ~850  $\Omega/\Box$  in the corresponding SIMS measured region. This way, the activation efficiency can be estimated as ~71%,  $\eta = \frac{600}{850} = 71\%$ .

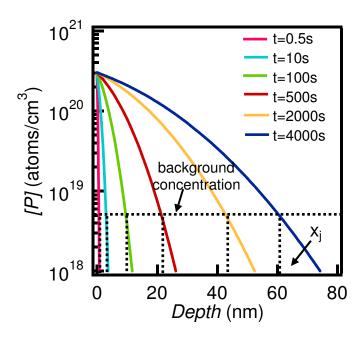

## Analytical constant-source diffusion modeling (P in Si)

Figure S2. Phosphorus profile of the constant-source diffusion model  $(N_o \sim 3x10^{20} \text{ cm}^{-3} \text{ and } D \sim 8x10^{16} \text{cm}^2 \text{ s}^{-1})$ .

For the constant-source diffusion, the dopant profile can be determined by the equation,  $N(x,t) = N_o erfc(\frac{x}{2\sqrt{Dt}})$ , where  $N_o$ , D and erfc are the surface concentration, diffusion coefficient and complementary error function, respectively. For example, Figure S2 illustrates the modeled profile for the phosphorus diffusion in silicon at 900°C for increasing diffusion time with the surface concentration  $(N_o)$  of ~3x10<sup>20</sup> cm<sup>-3</sup> and the diffusion coefficient (D) of ~8x10<sup>16</sup> cm<sup>2</sup> s<sup>-1</sup>. Each corresponding junction depth,  $x_j$ , can be determined at the baseline of the background concentration as  $5x10^{18}$  atoms/cm<sup>3</sup>. Then the sheet resistance,  $R_s$ , of each  $x_j$ , can be calculated using the Equation S1. As a result, the correlation between the  $R_s$  versus  $x_j$  for the constant-source diffusion model can be obtained.

## **Non Contact Junction Leakage Measurements**

**Figure S3.** Non-contact junction leakage (in  $\mu$ A/cm<sup>2</sup>) wafer mapping for P-MLD samples with spike anneal temperatures of (A) 900°C, (B) 950°C, (C) 1000°C and (D) 1050°C.

## Reference

S1. Zeghbroeck, B. V. *Principles of Semiconductor Devices*, **2004** (University of Colorado, http://ece-www.colorado.edu/~bart/book/book).