## High-gain monolithic 3D CMOS inverter using layered semiconductors

Angada B. Sachid, Sujay B. Desai, Ali Javey, and Chenming Hu Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, USA

(Received 14 September 2017; accepted 3 November 2017; published online 27 November 2017)

We experimentally demonstrate a monolithic 3D integrated complementary metal oxide semiconductor (CMOS) inverter using layered transition metal dichalcogenide semiconductor N-channel (NMOS) and P-channel (PMOS) MOSFETs, which are sequentially integrated on two levels. The two devices share a common gate. Molybdenum disulphide and tungsten diselenide are used as channel materials for NMOS and PMOS, respectively, with an ON-to-OFF current ratio ( $I_{ON}/I_{OFF}$ ) greater than 10<sup>6</sup> and electron and hole mobilities of 37 and 236 cm<sup>2</sup>/Vs, respectively. The voltage gain of the monolithic 3D inverter is about 45 V/V at a supply voltage of 1.5 V and a gate length of 1  $\mu$ m. This is the highest reported gain at the smallest gate length and the lowest supply voltage for any 3D integrated CMOS inverter using any layered semiconductor. *Published by AIP Publishing*. https://doi.org/10.1063/1.5004669

Device scaling has been essential to increase integration density in semiconductor circuits and systems with the accompanied benefits of higher speed and lower power dissipation.<sup>1</sup> With scaling, several second order effects such as variability, parasitic resistance, and parasitic device and interconnect capacitance are limiting the performance of the devices, circuits, and systems.<sup>2</sup> Monolithic 3-dimensional (3D) integration in which active device layers are sequentially fabricated can improve the circuit and system performance by reducing the average interconnect length and capacitance. thereby increasing the circuit speed and decreasing power dissipation.<sup>3</sup> 3D integration also enables the integration of heterogeneous active materials. To this effect, monolithic 3D integration of logic circuits, memory, and sensors was demonstrated. Layered transition metal dichalcogenides (TMDs) such as molybdenum disulphide (MoS<sub>2</sub>), tungsten diselenide (WSe<sub>2</sub>), and so on show promising electronic and optoelectronic properties.<sup>4</sup> TMDs allow precise thickness control down to a monolayer thickness (less than a nanometer), which could potentially solve an important problem in scaled devices, i.e., variation in the channel thickness in ultra-thin body devices.<sup>5</sup> Many of the TMD materials such as MoS<sub>2</sub> and WSe<sub>2</sub> have a lower dielectric constant, which can reduce the drain-to-channel coupling and hence improve the shortchannel performance of highly scaled devices.<sup>6</sup> The relative dielectric constant is  $\sim 10.7$  for the bulk and reduces to  $\sim 3.4$ for the monolayer thickness of MoS<sub>2</sub>. The in-plane and outof-plane dielectric constants of bulk MoS<sub>2</sub> are 7.43 and 15.4, respectively, and for monolayer MoS<sub>2</sub>, they are 1.63 and 7.36, respectively.<sup>7</sup> Transistors using MoS<sub>2</sub> and WSe<sub>2</sub> have shown low mobility degradation with a gate-to-channel electric field even at monolayer channel thickness.<sup>8–10</sup> A field-effect hole mobility as high as 300 cm<sup>2</sup>/Vs was reported for monolayer WSe<sub>2</sub> MOSFET.<sup>10</sup> Hence, monolithic 3D integration using TMDs is interesting for further scaling.

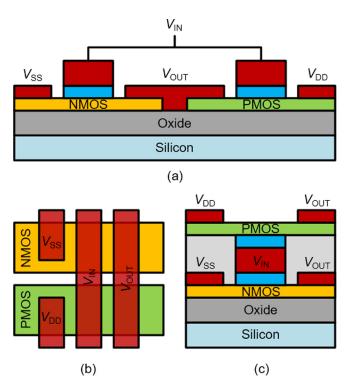

In the planar complementary metal oxide semiconductor (CMOS) static logic gates, the N-channel (NMOS) and the P-channel (PMOS) transistors are placed on the same plane. The gate, source, and drain electrodes are connected

appropriately to form the inverter circuit as shown in Fig. 1(a). It can be seen that a pair of NMOS and PMOS devices are present in the circuit, and electrically, they share the same gate electrode. A typical layout for the inverter is shown in Fig. 1(b). The NMOS and the PMOS share the gate electrode. In many circuits such as NAND, NOR, XOR, and XNOR, the source and drain electrodes cannot always be shared and must be electrically isolated as shown in the generalized device structure [Fig. 1(c)]. This type of shared gate 3D architecture was explored for silicon MOSFETs and FinFETs and TMDs.<sup>11,12</sup> To date, the only monolithic 3D integration using TMDs showed a CMOS inverter voltage

FIG. 1. (a) Planar implementation of the CMOS inverter. (b) Layout of a planar CMOS inverter. (c) Monolithic 3D CMOS inverter with the common gate and electrically isolated source/drain electrodes.

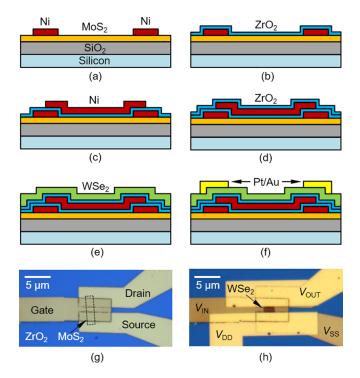

FIG. 2. Device fabrication flow: (a)  $MoS_2$  flake (thickness = 3.5 nm) on the Si/SiO<sub>2</sub> substrate after source/drain Ni contacts; (b) after  $ZrO_2$  deposition using ALD; (c) Ni top gate is formed; (d)  $ZrO_2$  is deposited using ALD; (e) WSe<sub>2</sub> flake (thickness = 2.8 nm) is placed on the gate stack using dry transfer; and (f) Pt/Au contacts are formed on WSe<sub>2</sub>. Optical image of the device after (g) S/D contacts and gate formation to MoS<sub>2</sub>; and (h) Pt/Au S/D formation on WSe<sub>2</sub>. WSe<sub>2</sub> MOSFET is fabricated right on top of the MoS<sub>2</sub> MOSFET. The gate length for NMOS and PMOS is 1  $\mu$ m.

gain  $(\Delta V_{\text{OUT}}/\Delta V_{\text{IN}})$  of about 10 V/V at a supply voltage  $(V_{\text{DD}})$  of 3 V.<sup>11</sup> In comparison to Ref. 11, in this work, we have added forming gas anneal, which is used as a cleaning step after the transfer of WSe<sub>2</sub>. Forming gas anneal was used to reduce the output conductance of the WSe<sub>2</sub> PMOS device and hence improve the voltage gain of the CMOS inverter. In this work, we report a high-gain monolithic 3D integrated common-gate CMOS inverter using MoS<sub>2</sub> as NMOS and WSe<sub>2</sub> as PMOS with a peak switching gain of about 45 V/V at  $V_{\text{DD}} = 1.5$  V, which is the highest reported gain at the smallest gate length and the lowest supply voltage for any reported 3D integrated CMOS inverter using any channel material.

Device fabrication was carried out on a p+ doped silicon substrate with 260 nm of silicon dioxide (SiO<sub>2</sub>). MoS<sub>2</sub> and

WSe<sub>2</sub> flakes were transferred onto the substrate using the mechanical exfoliation method. Flakes with 3 nm to 6 nm thickness were chosen for further device fabrication. The chosen MoS<sub>2</sub> flakes were etched into rectangular shapes using xenon difluoride (XeF<sub>2</sub>) gas.<sup>13</sup> 40 nm of nickel (Ni) was evaporated and lifted-off to form the source/drain contacts to  $MoS_2$  [Fig. 2(a)]. 1 nm of  $SiO_x$  was evaporated as the seeding layer, and 20 nm zirconium dioxide (ZrO<sub>2</sub>) deposited using atomic layer deposition (ALD) at 110 °C acts as the high- $\kappa$  gate oxide [Fig. 2(b)]. Figure 2(c) shows the first layer MoS<sub>2</sub> MOSFET with a 40 nm Ni metal common gate for the MoS<sub>2</sub> N-MOSFET in the first layer and the WSe<sub>2</sub> P-MOSFET that will be formed on top of the first layer. Next, 20 nm of ZrO<sub>2</sub> was deposited at 110 °C using ALD [Fig. 2(d)]. WSe<sub>2</sub> flake was transferred on top of the gate dielectric using a pick-and-place transfer method [Fig. 2(e)].<sup>8</sup> The flake was etched into a rectangular shape using  $XeF_2$  gas. At this stage, forming gas anneal was performed at 120 °C for 30 min. Forming gas anneal is known to remove organic residues.<sup>14</sup> Forming gas anneal helps to clean the surface of WSe<sub>2</sub>. 10 nm of platinum (Pt) and 30 nm of gold (Au) were evaporated and lifted-off to form the S/D contacts to WSe<sub>2</sub>. Figure 2(g) shows the device after the gate metal formation. Figure 2(h) shows the final device after S/D contacts are formed on WSe<sub>2</sub>.

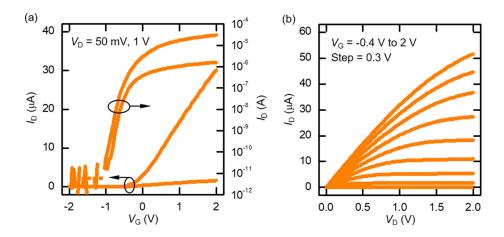

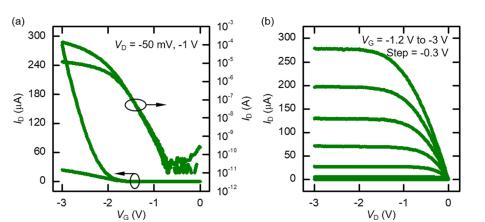

Figures 3 and 4 show the  $I_{\rm D} - V_{\rm G}$  and  $I_{\rm D} - V_{\rm D}$  characteristics of representative MoS2 NMOS and WSe2 PMOS devices, respectively. The threshold voltage  $(V_T)$  was extracted using the constant current method with a current reference of  $10^{-7}$  A/ $\mu$ m. For the MoS<sub>2</sub> NMOS, V<sub>T</sub> was extracted to be -0.56 V. The drain current at  $V_{\rm D} = 1$  V and  $V_{\rm G} - V_{\rm T} = 1$  V is about  $10 \,\mu\text{A}/\mu\text{m}$ . The  $I_{\text{ON}}/I_{\text{OFF}}$  ratio is over  $10^6$ . For the WSe<sub>2</sub> PMOS,  $V_{\rm T}$ , drain current at  $V_{\rm D} = -1$  V and  $|V_{\rm G} - V_{\rm T}| = 1$  V, and  $I_{\rm ON}/I_{\rm OFF}$  ratio are about -1.48 V, 50  $\mu$ A/ $\mu$ m, and 10<sup>7</sup>, respectively. The electron field-effect mobility for  $MoS_2$  was extracted to be  $37 \text{ cm}^2/\text{Vs}$ , and the hole field-effect mobility for WSe<sub>2</sub> was 236 cm<sup>2</sup>/Vs, which are commensurate with those reported in the literature.<sup>8–10,15</sup> The contact resistance of MoS<sub>2</sub> MOSFET is  $1.45 \text{ k}\Omega \mu \text{m}$  and that of WSe<sub>2</sub> MOSFET is  $1.04 \text{ k}\Omega \mu \text{m}$  on each side. The peak transconductance  $(g_m)$  for MoS<sub>2</sub> and WSe<sub>2</sub> MOSFETs is about  $15 \,\mu\text{S}/\mu\text{m}$  and  $42 \,\mu\text{S}/\mu\text{m}$ , respectively. The devices show excellent output saturation. The output conductance  $(g_{ds})$  at  $|V_G - V_T| = 1$  V for MoS<sub>2</sub> and WSe<sub>2</sub> MOSFETs is less than 1 nS/ $\mu$ m each. In Ref. 11, the output conductance

FIG. 3.  $I_{\rm D} - V_{\rm G}$  and  $I_{\rm D} - V_{\rm D}$  characteristics of MoS<sub>2</sub> N-MOSFET.

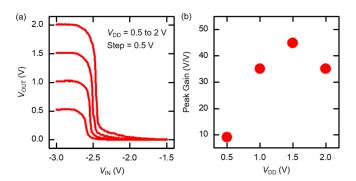

of the reported WSe<sub>2</sub> PMOS device was about 5  $\mu$ S/ $\mu$ m. The forming gas anneal step that was added after the transfer of WSe<sub>2</sub> helped to obtain a cleaner surface and improved the output conductance. The voltage gain for a CMOS inverter is  $(g_{mn} + g_{mp})/(r_{on}||r_{op})$ , where  $r_o$  is the output resistance of the device and the subscripts *n* and *p* refer to the NMOS and PMOS devices, respectively.<sup>16</sup> High  $g_m$  and  $r_o$  (=1/ $g_{ds}$ ) are required to achieve high switching voltage gain in a CMOS inverter. Figure 5 shows the voltage transfer characteristics and peak gain of a representative monolithic 3D integrated CMOS inverter. The highest peak gain of about 45 V/V is observed at  $V_{DD}$  = 1.5 V and gate length  $L_G$  = 1  $\mu$ m, which is the highest gain reported at the smallest gate length and the lowest supply voltage for a monolithic 3D CMOS inverter using any channel material. To use an inverter in a circuit,

FIG. 4.  $I_D - V_G$  and  $I_D - V_D$  characteristics of WSe<sub>2</sub> P-MOSFET.

FIG. 5. (a) Voltage transfer characteristics of the monolithic 3D CMOS inverter and (b) peak voltage gain as a function of supply voltage.

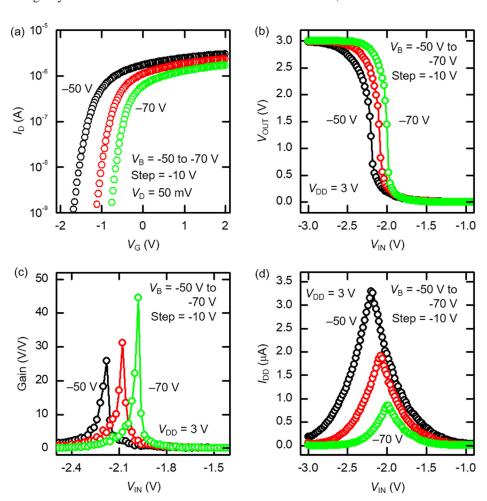

FIG. 6. (a)  $I_{\rm D} - V_{\rm G}$  characteristics as a function of  $V_{\rm B}$ . (b) Voltage transfer characteristics of a monolithic 3D CMOS inverter as a function of  $V_{\rm B}$ . (c) Voltage gain of the monolithic 3D CMOS inverter as a function of  $V_{\rm B}$ . (d) Current drawn from the supply voltage as a function of  $V_{\rm IN}$ .

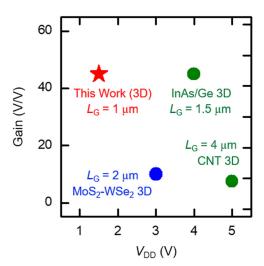

switching must be achieved between 0 and  $V_{\text{DD}}$ , preferably at around  $V_{DD}/2$ . The inverter shown in Fig. 5 does not switch between 0 and  $V_{DD}$  as the  $V_T$  of NMOS is negative. Hence, the noise margins for the inverter cannot be calculated. Methods such as gate work function engineering,<sup>17</sup> channel doping,<sup>9,16,18</sup> and local back biasing<sup>11,19</sup> can be used to achieve the correct  $V_{\rm T}$  for NMOS. Figure 6 shows the impact of substrate back-biasing  $(V_{\rm B})$  on the performance of MoS<sub>2</sub> NMOS and inverter. By applying a more negative back bias, the  $V_{\rm T}$  of the MoS<sub>2</sub> NMOS increases and becomes less negative. The  $V_{\rm T}$  changes from -1.32 V to -0.45 V when the back bias is changed from -50 V to -70 V, respectively. The back-bias-coefficient  $(\gamma = \delta V_{\rm T}/\delta V_{\rm B} = C_{\rm oxb}/C_{\rm oxf}$  $= t_{oxf}/t_{oxb}$ ) is about 44 mV/V, where the subscripts oxf and oxb refer to the front and back oxides, respectively.<sup>20</sup> The low  $\gamma$  is due to the thick SiO<sub>2</sub> layer and can be increased by decreasing the thickness of the SiO<sub>2</sub> layer. Substrate back bias shifts the switching point ( $V_{\rm IN}$  at  $V_{\rm OUT} = V_{\rm DD}/2$ ) of the inverter to more positive values of  $V_{\rm IN}$  as the  $V_{\rm T}$  of NMOS increases [Fig. 6(b)]. The switching point shifts by about 200 mV positive when the back bias changes from -50 V to -70 V. Voltage gain increases with the increase in RBB [Fig. 6(c)]. The voltage gains are 26 V/V, 31 V/V, and 45 V/ V at  $V_{\rm B} = -50$  V, -60 V, and -70 V, respectively. This shows that  $MoS_2$  NMOS with positive  $V_T$  can further improve the voltage gain of the monolithic 3D CMOS inverter. The inverter voltage gain is benchmarked against the other reported implementations of planar and 3D CMOS inverters.<sup>11,15,16,19,21,22</sup> Among all the reported monolithic 3D CMOS inverters using any channel materials, this work shows the highest voltage gain of 45 V/V, obtained at  $V_{\rm DD} = 1.5 \,\mathrm{V}$  and  $L_{\rm G} = 1 \,\mu\mathrm{m}$  (Fig. 7). Previously reported implementation of the MoS<sub>2</sub>-WSe<sub>2</sub> monolithic 3D CMOS inverter showed a voltage gain of 10 V/V at  $V_{\text{DD}} = 3 \text{ V.}^{11}$ The monolithic 3D CMOS inverter using InAs (NMOS)/Ge (PMOS) showed a voltage gain of 45 V/V at  $V_{DD} = 4$  V and  $L_{\rm G} = 1.5 \,\mu {\rm m.}^{23}$  The carbon nanotube (CNT)-based 3D CMOS inverter showed a gain of about 8 V/V at  $V_{\rm DD} = 5 \, {\rm V.}^{22}$  The gain of the inverter increases with the smaller channel length modulation parameter,  $\lambda$ , which is

FIG. 7. Benchmarking of our TMD monolithic 3D CMOS inverter against other reported 3D CMOS inverters. MoS<sub>2</sub>-WSe<sub>2</sub> 3D,<sup>11</sup> InAs/Ge 3D,<sup>23</sup> and CNT 3D.<sup>22</sup>

inversely proportional to the gate length ( $L_G$ ). CMOS inverters with longer  $L_G$  will show higher gain. Hence, this work shows the highest gain at the smallest gate length for a 3D CMOS inverter using any channel material.

Monolithic 3D integration is essential to increase the integration density accompanied by higher speed and lower power dissipation. We demonstrate a monolithic 3D integrated CMOS inverter using layered transition metal dichal-cogenides. For a monolithic 3D CMOS inverter using any layered semiconductor, we report the highest voltage gain of about 45 V/V, which is achieved at a supply voltage of 1.5 V and a gate length of 1  $\mu$ m.

This work was funded by Applied Materials, Inc. and Entegris, Inc. through the I-RiCE program.

<sup>1</sup>D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H.-S. P. Wong, Proc. IEEE **89**(3), 259 (2001).

<sup>2</sup>T. Skotnicki, C. Fenouillet-Beranger, C. Gallon, F. Bœuf, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, and F. Arnaud, IEEE Trans. Electron Devices **55**(1), 96 (2008); K. J. Kuhn, M. D. Giles, D. Becher, P. Kolar, A. Kornfeld, R. Kotlyar, S. T. Ma, A. Maheshwari, and S. Mudanai, *ibid.* **58**(8), 2197 (2011).

<sup>3</sup>A. W. Topol, D. C. La Tulipe, L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, and K. W. Guarini, IBM J. Res. Dev. 50(4.5), 491 (2006); D. J. Young, V. Malba, J. J. Ou, A. F. Bernhardt, and B. E. Boser, paper presented at the Electron Devices Meeting, 1997. IEDM '97 Technical Digest., International, 1997; C. C. Yang, J. M. Shieh, T. Y. Hsieh, W. H. Huang, H. H. Wang, C. H. Shen, T. T. Wu, Y. F. Hou, Y. J. Chen, Y. J. Lee, M. C. Chen, F. L. Yang, Y. H. Chen, M. C. Wu, and W. K. Yeh, paper presented at the 2015 IEEE International Electron Devices Meeting (IEDM), 2015; T. T. Wu, C. H. Shen, J. M. Shieh, W. H. Huang, H. H. Wang, F. K. Hsueh, H. C. Chen, C. C. Yang, T. Y. Hsieh, B. Y. Chen, Y. S. Shiao, C. S. Yang, G. W. Huang, K. S. Li, T. J. Hsueh, C. F. Chen, W. H. Chen, F. L. Yang, M. F. Chang, and W. K. Yeh, paper presented at the 2015 IEEE International Electron Devices Meeting (IEDM), 2015; T. T. Wu, W. H. Huang, C. C. Yang, C. D. Lin, H. H. Wang, C. H. Shen, and J. M. Shieh, paper presented at the 2015 International Symposium on VLSI Technology, Systems and Applications, 2015; H. Wei, M. Shulaker, H. S. Philip Wong, and S. Mitra, in 2013 IEEE International Electron Devices Meeting (IEDM), 2013; H. Wei, N. Patil, A. Lin, H. S. Philip Wong, and S. Mitra, paper presented at the 2009 IEEE International Electron Devices Meeting (IEDM), 2009; M. M. Shulaker, T. F. Wu, A. Pal, L. Zhao, Y. Nishi, K. Saraswat, H. S. Philip Wong, and S. Mitra, paper presented at the 2014 IEEE International Electron Devices Meeting (IEDM), 2014; M. M. Shulaker, K. Saraswat, H. S. P. Wong, and S. Mitra, paper presented at the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, 2014; C.-H. Shen, J.-M. Shieh, T.-T. Wu, W.-H. Huang, C.-C. Yang, C.-J. Wan, C.-D. Lin, H.-H. Wang, C. Bo-Yuan, and G.-W. Huang, paper presented at the 2013 IEEE International Electron Devices Meeting (IEDM), 2013; C.-H. Shen, J.-M. Shieh, W.-H. Huang, T.-T. Wu, C.-F. Chen, M.-H. Kao, C.-C. Yang, C.-D. Lin, H.-H. Wang, and T.-Y. Hsieh, paper presented at the 2014 IEEE International Electron Devices Meeting (IEDM), 2014; C. Liu and S. K. Lim, paper presented at the IEEE International Interconnect Technology Conference, 2012; P. Jin-Hong, T. Munehiro, K. Duygu, K. Pawan, H.-Y. Yu, H. S. Philip Wong, and K. C. Saraswat, paper presented at the IEEE International Electron Devices Meeting, 2008. IEDM, 2008; V. Deshpande, V. Djara, E. O. Connor, P. Hashemi, K. Balakrishnan, M. Sousa, D. Caimi, A. Olziersky, L. Czornomaz, and J. Fompeyrine, paper presented at the 2015 IEEE International Electron Devices Meeting (IEDM), 2015.

<sup>4</sup>M. Chhowalla, H. S. Shin, G. Eda, L.-J. Li, K. P. Loh, and H. Zhang, Nat. Chem. 5(4), 263 (2013); Q. H. Wang, K. Kalantar-Zadeh, A. Kis, J. N. Coleman, and M. S. Strano, Nat. Nanotechnol. 7(11), 699 (2012).

<sup>5</sup>X. Wang, A. R. Brown, B. Cheng, and A. Asenov, paper presented at the 2011 IEEE International Electron Devices Meeting (IEDM), 2011; A. B. Sachid, R. Francis, M. S. Baghini, D. K. Sharma, K. H. Bach, R. Mahnkopf, and V. R. Rao, paper presented at the 2008 IEEE International Electron Devices Meeting, 2008.

- <sup>6</sup>X. Zhang, D. O. Hayward, and D. M. P. Mingos, Catal. Lett. 84(3), 225 (2002); Y. Yoon, K. Ganapathi, and S. Salahuddin, Nano Lett. 11(9), 3768 (2011); S. Kim, A. Konar, W.-S. Hwang, J. H. Lee, J. Lee, J. Yang, C. Jung, H. Kim, J.-B. Yoo, J.-Y. Choi, Y. W. Jin, S. Y. Lee, D. Jena, W. Choi, and K. Kim, Nat. Commun. 3, 1011 (2012).

- <sup>7</sup>A. Molina-Sánchez and L. Wirtz, Phys. Rev. B 84(15), 155413 (2011).

- <sup>8</sup>T. Roy, M. Tosun, J. S. Kang, A. B. Sachid, S. B. Desai, M. Hettick, C. C. Hu, and A. Javey, ACS Nano 8(6), 6259 (2014).

- <sup>9</sup>H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, and A. Javey, Nano Lett. **12**(7), 3788 (2012).

- <sup>10</sup>A. B. Sachid, H. Fang, A. Javey, and C. Hu, in Proceedings of Technical Program-2014 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), 2014.

- <sup>11</sup>A. B. Sachid, M. Tosun, S. B. Desai, C.-Y. Hsu, D.-H. Lien, S. R. Madhvapathy, Y.-Z. Chen, M. Hettick, J. S. Kang, and Y. Zeng, Adv. Mater. 28, 2547–2554 (2016).

- <sup>12</sup>J. F. Gibbons and K. F. Lee, IEEE Electron Device Lett. 1(6), 117 (1980); J. P. Colinge and E. Demoulin, *ibid.* 2, 250 (1981); W. Xusheng, P. C. H. Chan, Z. Shengdong, F. Chuguang, and M. Chan, IEEE Trans. Electron Devices 52(9), 1998 (2005).

- <sup>13</sup>Y. Huang, J. Wu, X. Xu, Y. Ho, G. Ni, Q. Zou, G. K. W. Koon, W. Zhao, A. H. Castro Neto, and G. Eda, Nano Res. 6(3), 200 (2013).

- <sup>14</sup>A. Hsu, H. Wang, K. K. Kim, J. Kong, and T. Palacios, IEEE Electron Device Lett. 32(8), 1008 (2011).

- <sup>15</sup>M. Tosun, S. Chuang, H. Fang, A. B. Sachid, M. Hettick, Y. Lin, Y. Zeng, and A. Javey, ACS Nano 8(5), 4948 (2014).

- <sup>16</sup>L. Yu, A. Zubair, E. J. G. Santos, X. Zhang, Y. Lin, Y. Zhang, and T. Palacios, Nano Lett. **15**(8), 4928 (2015).

- <sup>17</sup>H. Wang, L. Yu, Y.-H. Lee, Y. Shi, A. Hsu, M. L. Chin, L.-J. Li, M. Dubey, J. Kong, and T. Palacios, Nano Lett. **12**(9), 4674 (2012).

- <sup>18</sup>D. Kiriya, M. Tosun, P. Zhao, J. S. Kang, and A. Javey, J. Am. Chem. Soc. **136**(22), 7853 (2014); K. Chen, D. Kiriya, M. Hettick, M. Tosun, T.-J. Ha, S. R. Madhvapathy, S. Desai, A. Sachid, and A. Javey, APL Mater. **2**(9), 092504 (2014).

- <sup>19</sup>S. Das, M. Dubey, and A. Roelofs, Appl. Phys. Lett. **105**(8), 083511 (2014).

- <sup>20</sup>G. Tsutsui, T. Nagumo, and T. Hiramoto, IEEE Trans. Nanotechnol. 2(4), 314 (2003).

- <sup>21</sup>J. Pu, K. Funahashi, C.-H. Chen, M.-Y. Li, L.-J. Li, and T. Takenobu, Adv. Mater. 28, 4111 (2016); L. Han, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P. D. Ye, ACS Nano 8(4), 4033 (2014); A. Pezeshki,

S. H. Hosseini Shokouh, P. J. Jeon, I. Shackery, J. S. Kim, I.-K. Oh, S. C. Jun, H. Kim, and S. Im, *ibid.* 10, 1118 (2016); P. J. Jeon, J. S. Kim, J. Y. Lim, Y. Cho, A. Pezeshki, H. S. Lee, S. Yu, S.-W. Min, and S. Im, ACS Appl. Mater. Interfaces 7(40), 22333 (2015); S. Das and A. Roelofs, paper presented at the Device Research Conference, 2014; J. Nah, H. Fang, C. Wang, K. Takei, M. H. Lee, E. Plis, S. Krishna, and A. Javey, Nano Lett. 12(7), 3592 (2012); A.-J. Cho, K. C. Park, and J.-Y. Kwon, Nanoscale Res. Lett. 10(1), 115 (2015); Z. Zhang, S. Wang, Z. Wang, L. Ding, T. Pei, Z. Hu, X. Liang, Q. Chen, Y. Li, and L.-M. Peng, ACS Nano 3(11), 3781 (2009); X. Liu, C. Lee, C. Zhou, and J. Han, Appl. Phys. Lett. 79(20), 3329 (2001); L. Ding, S. Liang, T. Pei, Z. Zhang, S. Wang, W. Zhou, J. Liu, and L.-M. Peng, Appl. Phys. Lett. 100(26), 263116 (2012); A. Javey, Q. Wang, A. Ural, Y. Li, and H. Dai, Nano Lett. 2(9), 929 (2002); Z. Zhang, X. Liang, S. Wang, K. Yao, Y. Hu, Y. Zhu, Q. Chen, W. Zhou, Y. Li, and Y. Yao, *ibid*. 7(12), 3603 (2007); K. Ryu, A. Badmaev, C. Wang, A. Lin, N. Patil, L. Gomez, A. Kumar, S. Mitra, H. S. Philip Wong, and C. Zhou, *ibid.* 9(1), 189 (2008); S. J. Kang, C. Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, S. V. Rotkin, and J. A. Rogers, Nat. Nanotechnol. 2(4), 230 (2007); D.-H. Kim, Y.-S. Kim, J. Wu, Z. Liu, J. Song, H.-S. Kim, Y. Y. Huang, K.-C. Hwang, and J. A. Rogers, Adv. Mater. 21(36), 3703 (2009); D.-H. Kim, J.-H. Ahn, H.-S. Kim, K. J. Lee, T.-H. Kim, C.-J. Yu, R. G. Nuzzo, and J. A. Rogers, IEEE Electron Device Lett. 29(1), 73 (2008); D.-H. Kim, J.-H. Ahn, W. M. Choi, H.-S. Kim, T.-H. Kim, J. Song, Y. Y. Huang, Z. Liu, C. Lu, and J. A. Rogers, Science 320(5875), 507 (2008); D.-H. Kim, W. M. Choi, J.-H. Ahn, H.-S. Kim, J. Song, Y. Huang, Z. Liu, C. Lu, C. G. Koh, and J. A. Rogers, Appl. Phys. Lett. 93(4), 044102 (2008); M. Lee, Y. Jeon, T. Moon, and S. Kim, ACS Nano 5(4), 2629 (2011); K. D. Buddharaju, N. Singh, S. C. Rustagi, S. H. G. Teo, L. Y. Wong, L. J. Tang, C. H. Tung, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, paper presented at the ESSDERC 2007-37th European Solid State Device Research Conference, 2007; K. D. Buddharaju, N. Singh, S. C. Rustagi, S. H. G. Teo, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, Solid-State Electron. 52(9), 1312 (2008); D. Wang, B. A. Sheriff, and J. R. Heath, Small 2(10), 1153 (2006); H. Wu, W. Wu, M. Si, and P. D. Ye, paper presented at the 2015 IEEE International Electron Devices Meeting (IEDM), 2015.

- <sup>22</sup>J.-H. Ahn, H.-S. Kim, K. J. Lee, S. Jeon, S. J. Kang, Y. Sun, R. G. Nuzzo, and J. A. Rogers, Science **314**(5806), 1754 (2006).

- <sup>23</sup>S. Nam, X. Jiang, Q. Xiong, D. Ham, and C. M. Lieber, Proc. Natl. Acad. Sci. **106**(50), 21035 (2009).