## High quality interfaces of InAs-on-insulator field-effect transistors with ZrO<sub>2</sub> gate dielectrics

Kuniharu Takei, <sup>1,2,3</sup> Rehan Kapadia, <sup>1,2,3</sup> Hui Fang, <sup>1,2,3</sup> E. Plis, <sup>4</sup> Sanjay Krishna, <sup>4</sup> and Ali Javey <sup>1,2,3,a)</sup>

<sup>1</sup>Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, USA

<sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, USA

<sup>3</sup>Berkeley Sensor and Actuator Center, University of California, Berkeley, California 94720, USA

<sup>4</sup>Electrical and Computer Engineering, University of New Mexico, Albuquerque, New Mexico 87106, USA

(Received 24 December 2012; accepted 26 March 2013; published online 19 April 2013)

Interface quality of InAs-on-insulator (XOI) field-effect transistors (FETs) with a  $ZrO_2$  gate dielectric is examined as a function of various chemical treatments. With a forming gas anneal, InAs XOI FETs exhibit a low subthreshold swing of  $\sim 72 \text{ mV/dec}$  with an interface trap density of  $\sim 1.5 \times 10^{12}$  states/cm<sup>2</sup> eV—both of which are comparable to the best reported epitaxially grown III-V devices on III-V substrates. Importantly, the results indicate that the surface properties of InAs are preserved during the layer transfer process, thereby, enabling the realization of high performance III-V FETs on Si substrates using the XOI configuration. © 2013 AIP Publishing LLC [http://dx.doi.org/10.1063/1.4802779]

III-V compound semiconductors present a promising class of materials for future low-power and high-speed electronics due to their low carrier effective mass and high mobilities.<sup>1–3</sup> Two promising approaches have been explored for integration of III-V semiconductors on Si wafers: (i) direct epitaxial growth on Si using buffer layers<sup>4</sup> and (ii) selective layer transfer from an epitaxial growth substrate onto a Si/ SiO<sub>2</sub> substrate.<sup>5,6</sup> The latter approach results in III-V on insulator (XOI) structures and presents the advantage of removing lattice mismatch constraints associated with the growth substrate. To date, high electron mobility InAs and InAsSb fieldeffect transistors (FETs);<sup>7,8</sup> high hole mobility InGaSb FETs;<sup>9</sup> and III-V complementary-FETs<sup>10</sup> have been demonstrated on Si substrates by using the XOI scheme. Despite these recent advancements, the dielectric and III-V interface quality is still largely unknown, and it remains a question whether similar interface qualities to direct epitaxial growth processes<sup>11</sup> can be obtained in XOI devices. Here, we focus on answering this question for InAs XOI FETs with ZrO2 gate dielectrics by examining the effect of various chemical treatments on the interface properties. Specifically, the subthreshold swing (SS) and interface trap density  $(D_{it})$  are systematically characterized by current-voltage  $(I-V_G)$ , capacitance-voltage  $(C-V_G)$ , and conductance-frequency  $(G/\omega - f)$  measurements. The longchannel devices treated under the optimal condition exhibit a SS as low as  $\sim$ 72 mV/decade and  $D_{\rm it}$  of  $\sim$ 1.5  $\times$  10<sup>12</sup> states/ cm<sup>-2</sup>eV, both of which are comparable to the best values reported for the epi-grown and/or bulk III-V devices.<sup>11</sup> The results demonstrate that high quality interfaces can be obtained in layer transferred InAs XOI structures, which is of fundamental importance for the practice use of this technology for future scaled transistors.

Ultrathin (~10 nm-thick) InAs films grown by a molecular beam epitaxy (MBE) on GaSb substrates with an AlGaSb sacrificial layer were transferred onto thermally grown  $SiO_2$

$(1.6 \,\mu\text{m} \text{ thick})$  on p<sup>+</sup>Si substrates using a previously described process.<sup>5</sup> Before transferring the InAs film to the Si/SiO<sub>2</sub> substrate, the back surface of the lifted-off InAs was cleaned with 1% HF in water to remove AlGaSb residues. After transferring the film onto the Si/SiO<sub>2</sub> substrate, the top surface of the InAs was cleaned with hot acetone at  $\sim 60 \,^{\circ}\text{C}$ to remove organic residues. Due to InAs native oxide formation during the fabrication process, the final thickness of InAs is  $\sim 8$  nm as confirmed by transmission electron microscopy. Ni source (S) and drain (D) electrodes were patterned, followed by contact annealing at 300 °C for 1 min in N<sub>2</sub> to obtain low contact resistances (~200-300  $\Omega$  µm) as previously reported.<sup>12</sup> A 10 nm-thick ZrO<sub>2</sub> film was deposited as the gate dielectric by atomic layer deposition (ALD) at 130 °C using tetrakis (ethylmethylamido) zirconium and water precursors. After ZrO<sub>2</sub> deposition, various thermal annealing and plasma treatments were performed, followed by an examination of the effect on the interface quality between InAs and ZrO<sub>2</sub> (i.e., top interface), InAs and SiO<sub>2</sub> (i.e., bottom interface), and the trap density in  $ZrO_2$ . The post-ALD thermal annealing was performed in either 5% H<sub>2</sub> in N<sub>2</sub> or 200 ppm H<sub>2</sub>S in N<sub>2</sub> for 30 min at 170 °C under atmospheric pressure. This temperature was chosen since thermal annealing at >170 °C resulted in noticeable degradation of InAs device properties (including SS) for both gas environments. No change in the contact resistance is observed after this step. In addition, samples exposed to  $CF_4/$  $O_2$  plasma (120 sccm CF<sub>4</sub>, 10 sccm  $O_2$ , 30 W, 3 min)<sup>11</sup> after ZrO<sub>2</sub> deposition were prepared and characterized. In addition to the above treatments, InAs XOI FETs with thermally grown oxide using  $2\% O_2$  in Ar at  $350 \degree C$  for 1 min before ZrO<sub>2</sub> deposition were prepared. Prior to the thermal oxidation, InAs native oxide was etched by 3% NH<sub>4</sub>OH in water. Our previous studies<sup>5</sup> have shown the thermal oxide of InAs to improve the SS of XOI FETs as compared to untreated samples and those with etched interfacial native oxide.

After the various surface/interface treatments, Ni/Au gate (G) electrodes were patterned and  $ZrO_2$  over the contact

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: ajavey@eecs.berkeley.edu

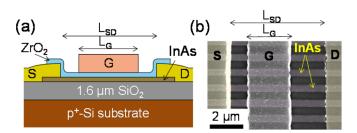

bonding pads was etched. Figure 1 shows a cross-sectional schematic of an InAs XOI FET on a Si substrate and a topview scanning electron microscopy (SEM) image of a representative device used in this study, depicting multiple InAs ribbons bridging the S/D contacts. XOI FETs with overlapped (i.e.,  $L_{SD} = L_G$ , where  $L_{SD}$  is the S/D spacing and  $L_G$ is the gate length) and underlapped (i.e.,  $L_G < L_{SD}$ ) gate structures were prepared. Current-gate voltage  $(I_{DS}-V_{GS})$ , capacitance-voltage  $(C-V_{GS})$ , and conductance-frequency  $(G/\omega - f)$  measurements were subsequently performed for each sample. Specifically, the underlapped gate structure was necessary to reduce G-S/D parasitic capacitances for C-V and  $G/\omega$ -f measurements. Note that for all devices, the ZrO<sub>2</sub> gate dielectric leakage currents were below the measurement set-up noise level for the applied voltage range of -2 V to 2 V.

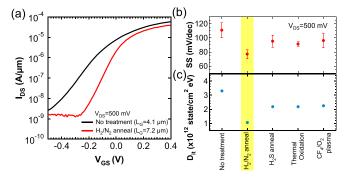

To examine the effect of various treatments on the interface properties, SS of XOI FETs was first systematically explored at room temperature. Figure 2(a) shows representative  $I_{DS}$ - $V_{GS}$  characteristics of overlapped gate InAs XOI FETs at  $V_{\rm DS} = 500 \,\mathrm{mV}$  fabricated with and without  $H_2/N_2$ forming gas anneal (FGA) after ALD of ZrO<sub>2</sub> gate dielectric. Clearly, a drastic improvement in the SS from  $\sim 110 \text{ mV/dec}$ to 72 mV/dec is observed by the FGA. Despite the relatively thick gate dielectric used here ( $\sim 10 \text{ nm}$  thick ZrO<sub>2</sub>), SS value of  $\sim$ 72 mV/decade is among the lowest values reported for III-V transistors to date, regardless of the device configuration. FGA is well known to fix the point defects at Si/SiO<sub>2</sub> interfaces,<sup>13</sup> even at low annealing temperatures.<sup>14</sup> Similarly, we hypothesize that the forming gas anneal used here reduces dangling bonds at InAs/ZrO2 and InAs/SiO2 interfaces in addition to reducing the trap density of ZrO2 gate dielectric (see supplementary material<sup>15</sup>). In the future, more detailed characterization of the chemical bonding at the interfaces is required to shed light on the observed behavior. It is worth noting that the peak effective mobility after FGA is  $\sim 2300 \text{ cm}^2/\text{Vs}$ , which is slightly higher than the mobility without annealing ( $\sim 2000 \text{ cm}^2/\text{Vs}$ ). This mobility improvement is attributed to the improved interface and reduced  $D_{it}$ .

Figure 2(b) shows the average SS and the standard deviation obtained from multiple devices (4–20) for each treatment condition. The average SS of untreated devices is  $111 \pm 10.6 \text{ mV/decade}$ . Overall, for all the treatments presented here, an improvement in SS is observed as compared to the untreated devices. The FGA treatment provides the best average SS of  $77 \pm 6.4 \text{ mV/dec}$  at  $V_{DS} = 500 \text{ mV}$ . Thermal oxidation of InAs provides the second best interface with a SS of  $92 \pm 3.2 \text{ mV/dec}$ . The thermal oxide of InAs is

FIG. 1. (a) Cross-sectional schematic of an ultrathin InAs XOI FET with an underlapped gate structure (i.e.,  $L_{\rm G} < L_{\rm SD}$ ). (b) SEM image of a representative device.

denser than the native oxide and under optimal conditions can cause surface restructuring of InAs.<sup>16</sup> Additionally, since sulfur passivation is well known to improve III-V surface/ interface properties;<sup>17</sup> here, we explored H<sub>2</sub>S gas annealing after ZrO<sub>2</sub> deposition. This treatment results in devices with SS = 95 ± 8.5 mV/dec. It is speculated that H<sub>2</sub>S diffuses to the InAs interfaces, causing sulfur passivation of InAs. With CF<sub>4</sub>/O<sub>2</sub> plasma treatment at room temperature after ZrO<sub>2</sub> deposition, the SS is ~96 ± 10.1 mV/dec. This fluorine termination results in similar properties as annealing in H<sub>2</sub>S gas.

Next, we quantify the density of interface traps for InAs XOI FETs as a function of surface/interface treatments using two different techniques. First,  $D_{it}$  is analytically extracted from SS using circuit models,<sup>18</sup> and  $G/\omega$ -f analysis is subsequently used to more directly assess  $D_{it}$  (Ref. 19). Figure 2(c) shows  $D_{it}$  extracted from SS for different treatments obtained from the following analytical expression:

$$SS = \frac{2.3kT}{q} \left( 1 + \frac{C_{it}}{C_{ZrO2}} + \frac{C_{body}}{C_{ZrO2}} - \frac{\frac{C_{body}^2}{C_{ZrO2}C_{SiO2}}}{1 + \frac{C_{it}}{C_{SiO2}} + \frac{C_{body}}{C_{SiO2}}} \right),$$

Here  $D_{it} = C_{it}/q$ , where  $C_{it}$  is the interface trap capacitance.  $C_{ZrO2} = 1.06 \times 10^{-6}$  F/cm<sup>2</sup> and  $C_{SiO2} = 2.16 \times 10^{-9}$  F/cm<sup>2</sup> were measured as the top and bottom oxide capacitances, respectively. InAs capacitance in the depletion regime,  $C_{body}$   $= \varepsilon_{InAs}/t_{InAs} \sim 1.67 \times 10^{-6}$  F/cm<sup>2</sup> was calculated using a dielectric constant of  $\varepsilon_{InAs} = 15.1$  and body thickness of  $t_{InAs} = 8$  nm by the parallel plate capacitance formula. k and q are Boltzmann constant and the electron charge, respectively. The lowest extracted  $D_{it}$  value is for samples annealed in forming gas with  $\sim 1.1 \times 10^{12}$  states/cm<sup>2</sup> eV.

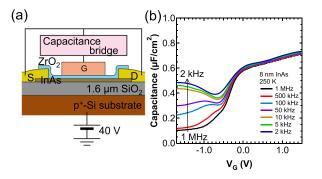

Next, detailed *C*-*V* measurements were used to characterize the interface properties. *C*-*V* measurements at the sample temperature of 250 K were conducted for XOI FETs with the underlapped gate structure as shown in Fig. 3(a). Note that the *C*-*V* measurements had to be performed at low temperatures in order to lower the thermal leakage current and noise in InAs which is a small band gap semiconductor. We focus on samples that were annealed in forming gas after ZrO<sub>2</sub> deposition since they exhibited the lowest SS. To

FIG. 2. (a)  $I_{DS}$ - $V_{GS}$  characteristics at  $V_{DS} = 500 \text{ mV}$  for two representative devices, with (red line;  $L_{G} \sim 7.2 \,\mu\text{m}$ ) and without (black line;  $L_{G} \sim 4.1 \,\mu\text{m}$ ) forming gas anneal after ALD of ZrO<sub>2</sub> gate dielectric. (b) Average SS and (c) extracted  $D_{\text{it}}$  of XOI FETs as a function of different surface/interface treatments.

FIG. 3. (a) Device structure and the measurement setup used for C-V and  $G/\omega$ -f measurements. (b) C-V characteristics at 250 K for an InAs XOI FET fabricated with post-ALD forming gas anneal. The DC amplitude is 50 mV.

reduce parasitic resistances from un-gated InAs channel region, global back-gate bias of 40 V is applied to p<sup>+</sup>Si substrate during both C-V and  $G/\omega$ -f measurements shown in Figs. 3 and 4 (see supplementary material<sup>15</sup>). Gate capacitance,  $C_G$ , was obtained from the accumulation region of *C-V* curves at  $V_G = 1.5$  V to be 0.73  $\mu$ F/cm<sup>2</sup> (Figure 3(b)).  $C_G$  consists of stack layers of ZrO<sub>2</sub> dielectric capacitance  $C_{ZrO2}$ , InAs charge centroid capacitance  $C_{centroid}$ , and density of state (DOS) quantum capacitance  $C_{Q-DOS}$  calculated by using the equation previously reported.<sup>9</sup> From our previous study,<sup>12</sup> the electron charge centroid of 8 nm InAs is  $t_{centroid} \sim 3.2 \text{ nm}$  from the top surface (at  $V_{G} \sim 1.5 \text{ V}$ ), giving  $C_{centroid} = \varepsilon_{InAs}/t_{centroid} \sim 4.18 \times 10^{-6} \text{ F/cm}^2$ . The total capacitance,  $1/C_G = 1/C_{ox} + 1/C_{centroid} + 1/C_{Q-DOS}$  is calculated to be ~ $6.1 \times 10^{-7}$  F/cm<sup>2</sup>, where  $C_{ox} = C_{ZrO2} = 1.06$  $\times 10^{-6}$  F/cm<sup>2</sup> and  $C_{Q-DOS} = 2.17 \times 10^{-6}$  F/cm<sup>2</sup>. The calculated  $C_G$  value matches with the experimental value (Fig. 3(b)). In the inversion region at  $V_{\rm G} < -0.5$  V, a large frequency dispersion of capacitance is observed. This trend is due to the lack of minority carrier (i.e., holes) response at high frequencies. The observed inversion behavior is similar to a conventional MOS capacitor. Note that unlike conventional MOSFETs, our XOI FETs consist of an n-channel body with ohmic metal S/D contacts to the conduction band

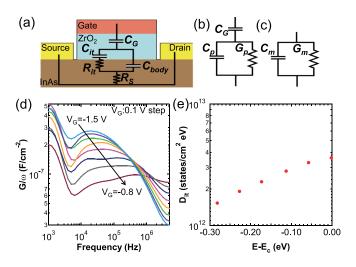

FIG. 4. (a) Equivalent circuit of an InAs XOI device. (b) Simplified circuit layout of (a). (c) Equivalent circuit as measured by the experimental set-up.  $C_{it}$  and  $R_{it}$  are interface trap capacitance and resistance, respectively.  $C_p$  is the equivalent parallel substrate capacitance. (d)  $G/\omega$  vs. frequency for the same device shown in Fig. 3. (e)  $D_{it}$  vs. E- $E_c$  calculated from the peak of  $G/\omega$ -f.

of InAs. While there are no Schottky barrier heights for electrons, the Schottky barrier height for holes is nearly the full band gap. Thereby, S/D contacts do not provide significant hole injection into the channel. This structural difference causes the observed frequency dispersion in the inversion regime.

To more carefully assess  $D_{\rm it}$ , the conductance method,<sup>19</sup>  $G/\omega$ -f, was utilized at 250 K sample temperature (Figs. 4(a)–4(c)). First to extract corrected capacitance  $C_c$  and conductance  $G_c$ , the series resistance  $R_s$  was calculated from the measured capacitance  $C_{ma}$  and conductance  $G_{\rm ma}$  in the accumulation region by using the following equation:

$$R_s = \frac{G_{ma}}{G_{ma}^2 + \omega^2 C_{ma}^2}.$$

Based on  $R_s$ , the series resistance factor was calculated as  $a = G_m \cdot (G_m^2 + \omega^2 C_m^2) R_s$ , where  $G_m$  and  $C_m$  are the measured conductance and capacitance. Then  $G_c$  and  $C_c$  were calculated by

$$G_{c} = \frac{(G_{m}^{2} + \omega^{2}C_{m}^{2})a}{a^{2} + \omega^{2}C_{m}^{2}}, \quad C_{c} = \frac{(G_{m}^{2} + \omega^{2}C_{m}^{2})C_{m}}{a^{2} + \omega^{2}C_{m}^{2}}$$

Finally  $G_p/\omega$  and  $D_{it}$  are described by the following equations:

$$\begin{aligned} \frac{G_p}{\omega} &= \frac{\omega G_c C_G^2}{G_c^2 + \omega^2 (C_G - C_c)^2},\\ D_{it} &= \frac{2.5}{q} \frac{G_p}{\omega}, \end{aligned}$$

where  $G_p$  is the equivalent parallel conductance. Based on these equations, first  $G_p/\omega f$  as a function of  $V_G$  bias from -0.8 V to -1.5 V was plotted in Fig. 4(d), followed by extracting  $D_{it}$  using peak  $G_p/\omega$  values. Figure 4(e) depicts that  $D_{it}$  at near mid-gap of InAs is around  $1.5 \times 10^{12}$  states/ cm<sup>-2</sup> eV, consistent with  $D_{it}$  extracted from SS (Fig. 2(b)). The extracted  $D_{it}$  arises from both top (ZrO<sub>2</sub>/InAs) and bottom (SiO<sub>2</sub>/InAs) interfaces due to ultrathin body (~8 nm) of InAs films. To better understand the origin of  $D_{it}$  in the XOI material system, back-side interface trap density measurement is also necessary; however, this is not possible with the current device structure and requires future studies.

Our measured  $D_{\rm it}$  value of  $\sim 1.5 \times 10^{12}$  states/cm<sup>-2</sup> eV for InAs XOI is comparable to previously reported values for high- $\kappa$  gate dielectrics on III-V bulk wafers or epitaxial thin films  $(D_{it} \sim 2 \times 10^{11} \text{ to } 6 \times 10^{12} \text{ states/cm}^{-2} \text{ eV}).^{11,20}$  The work here suggests that the layer transfer process does not degrade the interface properties of InAs. The finding is rather surprising given that both top and bottom surfaces of InAs are exposed to various organic materials and wet etchants during the transfer process. The results suggest that the InAs surface is robust, at least in terms of  $D_{it}$ . An explanation for this result may be that the Fermi stabilization energy of InAs lies deep in the conduction band,<sup>21</sup> indicating that native defects create electronic states with average energy in the conduction band, thereby, causing minimal degradation on the FET properties, especially the SS. Although the measured  $D_{it}$  values here are low for III-V FET standards, they are still large compared to Si devices. However, our lowest SS is  $\sim$ 72 mV/decade, which is close to the MOSFET ideal limit, despite the relatively thick gate dielectric used here. In the future, SS can be further improved by using a thinner top gate dielectric.

In summary, through subthreshold swing analyses, and *C-V* and *G/\omega-f* measurements, the surface/interface properties of InAs XOI FETs on Si substrates are characterized as a function of various treatments. It is found that FGA after the deposition of the ZrO<sub>2</sub> gate dielectric significantly improves SS of XOI FETs, with the lowest value of ~72 mV/dec, which is close to the theoretical limit of ~60 mV/decade. The  $D_{it}$  value was extracted to be ~1.5 × 10<sup>12</sup> states/ cm<sup>-2</sup> eV near the mid-gap of InAs. These results indicate that the overall quality of InAs surfaces is preserved during the layer transfer process.

This work was funded by NSF E3S Center and Intel. The materials characterization part of this work was partially supported by the Director, Office of Science, Office of Basic Energy Sciences, and Division of Materials Sciences and Engineering of the U.S. Department of Energy under Contract No. De-Ac02-05Ch11231. A.J. acknowledges support from the World Class University program at Sunchon National University. K.T. acknowledges funding from NSF COINS. S.K. acknowledges support from AFOSR FA9550-10-1-0113 and FA9550-09-1-0231.

- <sup>1</sup>D.-H. Kim and J. A. del Alamo, IEEE Trans. Electron Devices **57**, 1504 (2010).

- <sup>2</sup>J. A. del Alamo, Nature (London) **479**, 317 (2011).

- <sup>3</sup>M. Heyns and W. Tsai, MRS Bull. **34**, 485 (2009).

- <sup>4</sup>M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J.

- M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard,

- N. Mukherjee, W. Rachmady, UShah, and R. Chau, Tech. Dig. Int. Electron Devices Meet. **2009**, 319.

- <sup>5</sup>H. Ko, K. Takei, R. Kapadia, S. Chuang, H. Fang, P. W. Leu, K. Ganapathi, E. Phis, H. S. Kim, S.-Y. Chen, M. Madsen, A. C. Ford, Y.-L. Chueh, S. Krishna, S. Salahuddin, and A. Javey, Nature (London) **468**, 286 (2010).

- <sup>6</sup>M. Yokoyama, T. Yasuda, H. Takagi, N. Miyata, Y. Urabe, H. Ishii, H. Yamada, N. Furuhara, M. Hata, M. Sugiyama, Y. Nakano, M. Takenaka, and S. Takagi, Appl. Phys. Lett. **96**, 142106 (2010).

- <sup>7</sup>K. Takei, S. Chuang, H. Fang, R. Kapadia, C.-H. Liu, J. Nah, H. S. Kim, E. Plis, S. Krishna, Y.-L. Chueh, and A. Javey, Appl. Phys. Lett. **99**, 103507 (2011).

- <sup>8</sup>H. Fang, S. Chuang, K. Takei, H. S. Kim, E. Plis, C.-H. Liu, S. Krishna, Y.-L. Chueh, and A. Javey, IEEE Electron Device Lett. **33**, 504 (2012).

- <sup>9</sup>K. Takei, M. Madsen, H. Fang, R. Kapadia, S. Chuang, H. S. Kim, C.-H. Liu, E. Plis, J. Nah, S. Krishna, Y.-L. Chueh, J. Guo, and A. Javey, Nano Lett. **12**, 2060 (2012).

- <sup>10</sup>J. Nah, H. Fang, C. Wang, K. Takei, M. H. Lee, E. Plis, S. Krishna, and A. Javey, Nano Lett. **12**, 3592 (2012).

- <sup>11</sup>Y.-T. Chen, Y. Wang, F. Xue, F. Zhou, and J. C. Lee, IEEE Trans. Electron Devices **59**, 139 (2012).

- <sup>12</sup>K. Takei, H. Fang, S. B. Kumar, R. Kapadia, Q. Gao, M. Madsen, H. S. Kim, C.-H. Liu, Y.-L. Chueh, E. Plis, S. Krishna, H. A. Bechtel, J. Guo, and A. Javey, Nano Lett. **11**, 5008 (2011).

- <sup>13</sup>A. Stesmans and V. V. Afanas'ev, Phys. Rev. B 57, 10030 (1998).

- <sup>14</sup>L. Do Thanh and P. Balk, J. Electrochem. Soc. 135, 1797 (1988).

- <sup>15</sup>See supplementary material at http://dx.doi.org/10.1063/1.4802779 for back-gate dependence of the devices and the effect of the forming gas annealing on  $ZrO_2$  film quality.

- <sup>16</sup>M. P. J. Punkkinen, P. Laukkanen, J. Lang, M. Kuzmin, M. Tuominen, V. Tuominen, J. Dahl, M. Pessa, M. Guina, K. Kokko, J. Sadowski, B. Johansson, I. J. Vayrynen, and L. Vitos, Phys. Rev. B 83, 195329 (2011).

- <sup>17</sup>E. O'Connor, B. Brennan, V. Djara, K. Cherkaoui, S. Monaghan, S. B. Newcomb, R. Contreras, M. Milojevic, G. Hughes, M. E. Pemble, R. M. Wallace, and P. K. Hurley, J. Appl. Phys. **109**, 024101 (2011).

- <sup>18</sup>J. P. Colinge, D. Flandre, and F. Van de Wiele, Solid-State Electron. 37, 289 (1994).

- <sup>19</sup>E. H. Nicollian and A. Goetzberger, Appl. Phys. Lett. **10**, 60 (1967).

- <sup>20</sup>Y. Hwang, V. Chobpattana, J. Y. Zhang, J. M. LeBeau, R. Engel-Herbert, and S. Stemmer, Appl. Phys. Lett. 98, 142901 (2011).

- <sup>21</sup>W. Walukiewicz, Physica B **302–303**, 123 (2001).