## Short-Channel Transistors Constructed with Solution-Processed Carbon Nanotubes

Sung-Jin Choi,<sup>†,⊥</sup> Patrick Bennett,<sup>†,⊥</sup> Kuniharu Takei,<sup>†</sup> Chuan Wang,<sup>†</sup> Cheuk Chi Lo,<sup>†</sup> Ali Javey,<sup>†</sup> and Jeffrey Bokor<sup>†,‡,\*</sup>

<sup>†</sup>Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, United States and <sup>‡</sup>Molecular Foundry, Lawrence Berkeley National Laboratory, Berkeley, California 94720, United States. <sup>⊥</sup>These authors contributed equally to this work.

**ABSTRACT** We develop short-channel transistors using solutionprocessed single-walled carbon nanotubes (SWNTs) to evaluate the feasibility of those SWNTs for high-performance applications. Our results show that even though the intrinsic field-effect mobility is lower than the mobility of CVD nanotubes, the electrical contact between the nanotube and metal electrodes is not significantly affected. It is this contact resistance which often limits the performance of ultrascaled transistors. Moreover, we found that the contact resistance is lowered by the introduction of oxygen

treatment. Therefore, high-performance solution-processed nanotube transistors with a 15 nm channel length were obtained by combining a top-gate structure and gate insulators made of a high-dielectric-constant ZrO<sub>2</sub> film. The combination of these elements yields a performance comparable to that obtained with CVD nanotube transistors, which indicates the potential for using solution-processed SWNTs for future aggressively scaled transistor technology.

**KEYWORDS:** carbon nanotubes · short channel · transistor · ballistic · solution-processed carbon nanotubes · contact resistance · quantum limit

he exceptional electronic properties of single-walled carbon nanotubes (SWNTs) make them promising building blocks for future nanoelectronic devices primarily because they perfectly combine the following traits: one-dimensional transport, small size, extremely high carrier mobility, large current density, small intrinsic gate delay, and high intrinsic cutoff frequency.<sup>1</sup> Clean and defect-free SWNTs are desirable for fabricating high-quality devices. Therefore, the high-temperature growth of SWNTs directly onto a substrate via chemical vapor deposition (CVD) has become the most widely used technique for achieving high-quality SWNT devices.<sup>2-5</sup> Devices formed via the CVD method possess excellent field-effect transistor (FET) properties with typical mobilities ranging from 1000 to 10 000 cm<sup>2</sup>/(V  $\cdot$  s), depending upon the diameter of the nanotubes,<sup>6</sup> and conductances approaching the ballistic limit (G = $4e^2/h \approx 155 \,\mu$ S).<sup>3,7</sup> However, the CVD process yields a mixture of metallic (m-SWNTs) and semiconducting (s-SWNTs) nanotubes, and m-SWNTs are an unacceptable contamination for digital electronics applications. Moreover, an effective method for selectively removing m-SWNTs after their growth without affecting neighboring s-SWNTs has not yet been established on a large scale.<sup>8</sup>

Solution-processed SWNTs offer an attractive alternative to separating SWNTs according to their electronic type in solution using techniques such as density gradient ultracentrifugation,<sup>9,10</sup> selective polymer wrapping,<sup>11</sup> and chromatography.<sup>12,13</sup> However, solution-processing techniques can introduce defects that degrade the intrinsic electrical properties of the SWNTs with a reported average effective mobility for s-SWNTs ranging from 20 to 300 cm<sup>2</sup>/(V·s),<sup>14-20</sup> which could limit their application in future nanoelectronic devices. Nevertheless, for short-channel nanotube transistors operating in the quasi-ballistic regime, in which electron transport is primarily limited by the contacts, transistors made from

\* Address correspondence to jbokor@eecs.berkeley.edu.

Received for review November 13, 2012 and accepted December 21, 2012.

Published online December 21, 2012 10.1021/nn305277d

© 2012 American Chemical Society

VOL.7 • NO.1 • 798-803 • 2013

solution-processed s-SWNTs can be expected to provide high performance if the quality of the metal contact with these nanotubes is comparable to that of the CVD nanotubes.<sup>20</sup> In the current work, we report the integration of 15 nm gate length ( $L_G$ ) short-channel solution-processed SWNT transistors into a top-gate structure with a high- $\kappa$  (ZrO<sub>2</sub>) gate dielectric layer. The objective of this work is to assess the feasibility of using solution-processed nanotubes in scaled FETs. The results confirm that the performance of the scaled solutionprocessed nanotube devices approaches the best p-type devices containing CVD nanotube channels.

## **RESULTS AND DISCUSSION**

The devices used in this work were composed of a purified, commercially available 90% semiconducting SWNT solution (0.01 mg/mL, average diameter ranging from 1.2 to 1.7 nm, determined by the commercial provider, Nano Integris Inc.) bridging metal source (S) and drain (D) electrodes on a SiO<sub>2</sub> (55 nm)/p<sup>+</sup>-Si substrate. We employed the spin alignment technique to partially align the nanotubes on the substrate.<sup>15</sup> The hydrodynamic flow, which has been shown to efficiently align nanoparticles on a drying surface,<sup>21</sup> appears to be markedly enhanced by the spinning wafer and effectively aligns the nanotubes as the solvent evaporates and thins.<sup>22</sup> The degree of alignment and number of nanotubes can be tuned based on the spinassembly conditions, such as spin speed and solution volume.<sup>15,23</sup> We first fixed the nanotube deposition conditions at a spin speed of 7000 rpm and varied a nanotube solution volume of 4  $\mu$ L to obtain a large number of devices with single nanotube channels. For multiple nanotube channels, we simply increased the volume of nanotube solution up to 6  $\mu$ L.

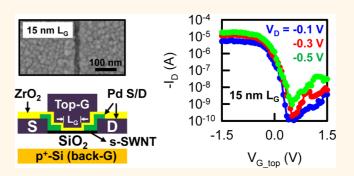

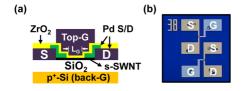

Figure 1. (a) Device schematic for the top-gate solutionprocessed SWNT transistor. (b) Optical image of such devices fabricated on the chip. After depositing the solution-processed nanotubes, a two-step source/drain (S/D) metallization (optical and e-beam lithography) of Pd was used to form the bottom-gate transistors. The bottom-gate transistors (Si as the back gate) were first characterized via electrical transport measurements before being subjected to atomic-layer deposition (ALD) of a ZrO<sub>2</sub> film ( $\kappa \approx 12$ ) for a single nanotube channel transistor using a tetrakis (ethylmethylamido) zirconium precursor and water at 130 °C.<sup>24</sup> After that, Pd gate electrodes were patterned for the top-gate structures.

A schematic of the device structure is shown in Figure 1a. Note that our top-gate device differs from self-aligned nanotube transistors<sup>25</sup> in that this device has ungated regions on two sides of the S/D electrodes. However, these ungated regions cannot significantly affect the carrier transport because top-gate can still modulate these areas through the strong fringing field. The minimum  $L_G$  value in this study is 15 nm. Figure 1b shows an optical microscope image of the fabricated top-gate transistors.

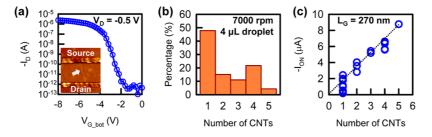

When packing numerous SWNTs into a device, the predicted on-current  $(I_{ON})$  is often hampered by charge screening.<sup>26</sup> Such screening is part of the reason why transistors from solution-processed nanotubes exhibited lower-than-anticipated on-currents.<sup>14</sup> However, the modest SWNT densities from the spin-aligned deposition used in this work provide an excellent platform for observing direct on-current scaling. Representative transfer characteristics for a bottom-gate FET with  $V_{\rm D} = -0.5$  V are shown in Figure 2a. This device has an  $L_G$  of 270 nm (in a bottom-gate device, an  $L_G$  is defined by the distance between S/D electrodes) with only a single nanotube (confirmed by AFM tapping mode) with an  $I_{ON}/I_{OFF}$  ratio in excess of 10<sup>6</sup>. Approximately 50% of the devices contained a single nanotube channel when the spin speed was 7000 rpm and the volume of the nanotube solution was 4  $\mu$ L (Figure 2b). Figure 2c shows a plot of the *I*<sub>ON</sub> versus the number of s-SWNTs from different devices. Note that some of the nanotubes for the multichannel device are m-SWNTs and such devices were excluded in this plot. The trend is linear, which represents direct on-scaling similar to previous reports for CVD nanotubes.<sup>27</sup> The deviation of

Figure 2. The electrical properties of the bottom-gate solution-processed SWNT transistors with  $L_{\rm G}$  = 270 nm. (a) Transfer characteristics at  $V_{\rm D}$  = -0.5 V. (Inset) AFM image of the device. (b) Probability for the number of SWNTs bridging the S/D electrodes at 7000 rpm with a volume of 4  $\mu$ L of the nanotube solution. (c)  $I_{\rm ON}$  versus the number of SWNTs from a set of bottom-gate devices under the same bias conditions ( $V_{\rm G}$  = -8 V and  $V_{\rm D}$  = -0.5 V).

VOL.7 • NO.1 • 798-803 • 2013 A

799

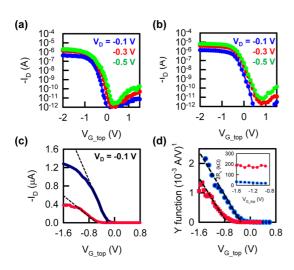

Figure 3. Transfer characteristics for the top-gate device with a single SWNT channel with  $L_{\rm G} = 240$  nm at different  $V_{\rm D}$ for the as-made device (a) and the device after oxygen treatment (b). The 15 nm ZrO<sub>2</sub> film (EOT  $\approx$  4.9 nm) was used as a gate dielectric. (c) Linear transfer characteristics for the two devices shown in Figure 3 (red line, as-made device; blue line, device after oxygen treatment) at  $V_{\rm D} = -0.1$  V. The black dotted lines serve as a visual guide. (d) The calculated Y-function and 2R<sub>c</sub> for the two devices made from solutionprocessed SWNTs with  $L_{G} = 240$  nm, shown in frame c, as a function of  $V_{G}$  (red symbol, as-made device; blue symbol, device after oxygen treatment). The black dotted lines represent the linear fits.

the data points from this linear relationship is most likely due to the variation in the SWNT diameters, which results in different band gaps and, thus, Schottkybarrier heights. Ideally, further work should tighten the distribution of the nanotube diameters and further increase the s-SWNT density while maintaining even spacing to prevent charge screening.

Next, we conducted systematic electrical transport measurements of the top-gate solution-processed device. Figure 3a shows the representative transfer characteristics for an as-fabricated top-gate device in air at room temperature with no further passivation or annealing treatments. This top-gate device was further processed from the bottom-gate devices with a single nanotube channel. The back-gate bias was floated in all measurements of the top-gate devices. The different  $L_{G}$ values between Figure 2 (270 nm) and Figure 3 (240 nm) arose from the different definition of  $L_{G}$ between bottom- and top-gate structures. For 15 nm thick  $ZrO_2$  gate dielectric layers, an  $L_G$  of a top-gate structure is defined by the gate electrode, that is,  $L_{G} =$  $270 - (2 \times 15) = 240$  nm. Note that both the subthreshold swing and the transconductance drastically improved from the bottom-gate device because of the thinner high- $\kappa$  gate dielectrics and top-gate structures. However, the current drivability was not significantly enhanced for the device as-made (Figure 3a). We did observe that the electrical performance of the top-gate device were substantially improved (Figure 3b) after oxygen exposure in the chamber at 230 mTorr for

50 min (we called this process "oxygen treatment"). The device after oxygen treatment exhibited a maximum transconductance ( $g_{\rm m} = dI_{\rm D}/dV_{\rm G}|V_{\rm D}$ )  $\approx$  8.6  $\mu$ S and  $I_{\rm ON} \approx -5.8 \ \mu {\rm A}$  (defined as  $|V_{\rm G} - V_{\rm T}| = 1.0 \ {\rm V}$  and  $V_{\rm D}$  = -0.5 V). The  $g_{\rm m}$  and  $I_{\rm ON}$  values were improved by 360% and 340%, respectively, after oxygen treatment. The subthreshold swing of the device was  $\sim$ 130 mV/decade, the  $I_{OFF}$  in  $I_D - V_G$  was relatively biasindependent (for  $V_D = -0.1$  V to -0.5 V), and the  $I_{\rm ON}/I_{\rm OFF}$  remained constant at ~10<sup>5</sup>.

It is interesting to investigate the effect of oxygen treatment on our top-gate devices. The effect of oxygen on the electrical properties of the nanotube devices has been reported previously, and was attributed to an increase in the work-function of metal contacts with the adsorption of oxygen molecules<sup>28</sup> To evaluate the oxygen effect on our top-gate structure, we introduced the Y-function method to obtain contact resistance and mobility values with the assumption of ohmic contacts and drift-diffusion as dominant carrier transports in long channel devices.<sup>20,29</sup> The Y-function is defined as follows:

$$Y = \frac{I_{\rm D}}{g_{\rm m}^{1/2}} = \left(\frac{W}{L} C_{\rm OX} \mu_{\rm FE} V_{\rm D}\right)^{1/2} (V_{\rm G} - V_{\rm T})$$

$$= \left(\frac{1}{L^2} C_{\rm G} \mu_{\rm FE} V_{\rm D}\right)^{1/2} (V_{\rm G} - V_{\rm T})$$

(1)

where we extracted the mobility  $(\mu_{FE})$  from the slope of the Y versus  $V_{\rm G}$  plot, with the intrinsic  $V_{\rm T}$  coming from the x-axis intercept. From the known  $\mu_{FE}$  and  $V_{T}$ , the contact resistance  $(R_c)$  of a specific device can be acquired from the following:

$$2R_{\rm C} = \frac{V_{\rm G}}{I_{\rm D}} - R_{\rm ch} = \frac{V_{\rm G}}{I_{\rm D}} - \frac{L_{\rm G}^2}{\mu_{\rm FE}C_{\rm G}(V_{\rm G} - V_{\rm T})}$$

(2)

Linear-scale transfer curves for two top-gate transistors, that is, with and without oxygen treatment, are shown in Figure 3c. These devices yield very different values for  $g_{\rm m}$ , which results in differing slopes for the linear scale. However, the plot of the Y-function for these devices reveal that they have nearly identical  $\mu_{\rm FE}$  values, as indicated by their similar slopes (Figure 3d), which results in a similar extracted  $\mu_{\text{FF}}$ of  $\sim$ 380 cm<sup>2</sup>/(V·s). This value is lower than the previously reported average for CVD nanotubes, which is typically in the range of  $1500-3000 \text{ cm}^2/(V \cdot s)$ , extracted from individual nanotube devices with similar submicrometer  $L_{G}$ .<sup>1,5,30,31</sup> These results indicate that relative to CVD nanotubes, solution-processed SWNTs can possess some structural defects induced during the purification and suspension processes, which limit  $\mu_{\rm FE}$ . However, we observe that the  $R_{\rm c}$  values of the oxygen-treated device were significantly lower than those of the as-made device. The inset of Figure 3d presents the calculated  $2R_c$  as a function of the  $V_G$ according to eq 2. Note that the lowered contact

VOL.7 • NO.1 • 798-803 • 2013

JAI

resistance values ( $2R_c = 20 - 34 \text{ k}\Omega$ ) were almost similar to those reported in previous studies of CVD nanotubes. Therefore, the solution-processed nanotubes are expected to perform similarly to CVD nanotubes in the final scaled FETs, in which electron transport is largely limited by the contacts rather than the channel scattering. We speculate that similar but slightly higher  $2R_c$  values in this work as compared to those in the best-reported CVD nanotube devices<sup>30,32</sup> are possibly due to remaining surfactants on the nanotube surface.

The lower  $R_c$  after oxygen treatment can be explained as follows. It has been reported that exposure of the device to oxygen could increase the workfunction of the metal surface.<sup>28</sup> An increased workfunction modifies the barrier at the metal-semiconducting nanotube interface and allows for efficient carrier transport. Oxygen molecules can desorb from the nanotube contacts during our ALD process for the ZrO<sub>2</sub> gate dielectrics due to the high process temperature (130 °C) and ambient vacuum. Although the devices are capped with the ZrO<sub>2</sub> gate dielectric layers, these layers are permeable enough to allow oxygen molecules to escape from and penetrate into the nanotube contacts to some extent. However, exposure to oxygen molecules in air is insufficient to produce high-performance devices, as shown in Figure 3a. Furthermore, to improve the electrical properties, long-time exposure in air should be required, but it is inefficient. Therefore, a reproducible improvement in the transistor performance is obtained for our top-gate structures through our oxygen treatment. Therefore, we conclude that oxygen treatment can effectively improve the performance of the device by reducing the contact resistance associated with the S/D electrodes.

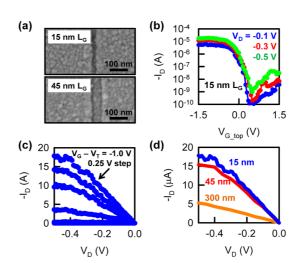

To observe the scaling behavior of the solutionprocessed nanotube devices, we first scaled the  $L_{G}$  to 15 nm for a single nanotube channel. In this case, reduced ZrO<sub>2</sub> film thickness of 10 nm was used for the gate dielectric (equivalent oxide thickness, EOT pprox3.2 nm). We also used oxygen treatment to enhance the electrical properties, such as  $g_m$  and  $I_{ON}$  values. Top-view SEM images of 15 and 45 nm  $L_{G}$  devices are shown in Figure 4a. Our representative miniaturized 15 nm  $L_{G}$  top-gate device with a single solutionprocessed SWNT exhibited a high peak transconductance of 32  $\mu$ S per tube,  $I_{ON}/I_{OFF} > 10^4$  at  $V_D = -0.5$  V, and a subthreshold swing of  $\sim$ 130 mV/dec (Figure 4b,c). The notable properties of the device were that its saturation current reached as high as  $\sim$ 17  $\mu$ A at  $|V_G - V_T| = 1.0$  V. As shown in Figure 4d, the saturation current was significantly improved when the channel was scaled down to 15 nm. The improvement from the L<sub>G</sub> scaling primarily relates to the suppression of scattering within the channel, and the nanotube device nearly reached the ballistic transport limit.<sup>25</sup>

Figure 4. Short-channel device with a single solution-processed SWNT. The 10 nm ZrO<sub>2</sub> film (EOT  $\approx$  3.2 nm) was used as a gate dielectric. (a) Top-view SEM images of the devices ( $L_{\rm G}$  = 15 and 45 nm). (b) Transfer characteristic for a device with  $L_{\rm G}$  = 15 nm at  $V_{\rm D}$  = -0.1 V, -0.3 V, and -0.5 V. (c) Output characteristics of the same device. The gate overdrive voltage was changed from 1.0 V in -0.25 V steps. (d) Output characteristics at the same gate overdrive voltage ( $|V_{\rm G} - V_{\rm T}|$  = 1.0 V) for the devices with different  $L_{\rm G}$ .

These results are significantly improved over those from the best solution-processed nanotube transistors reported to date.<sup>16,17,19,20,33</sup> Furthermore, Figure 4d shows how L<sub>G</sub> scaling affects the low-field slope and saturation current. Note how similar the curves are for 15 and 45 nm  $L_{G}$  devices, indicating that at low fields, scattering in the channel plays a minor role in device performance. This is evidence of reaching ballistic channel transport (negligible channel resistance) and is consistent with previous reports on CVD nanotubes.<sup>25,30,32</sup> However, relatively higher subthreshold slope, lower saturation current, and lower transconductance values in our device, compared to the CVD nanotube devices, 25,30,32 can be attributed to the thicker EOT. Therefore, we anticipate an improved switching behavior will be obtained for the current device when using thinner high- $\kappa$  gate dielectrics.

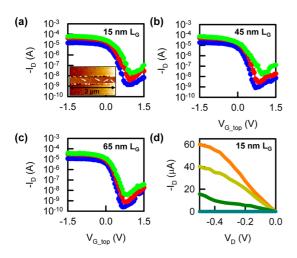

We further developed highly scaled devices with multiple solution-processed nanotube channels. Those transistors were fabricated in different batches. The volume of the nanotube solution for the spin alignment technique increased from 4 to 6  $\mu$ L to obtain a large amount of multiple nanotube channels. The average number of nanotubes inside the channel with 2  $\mu$ m width is estimated as 3–4 from the test structure (inset of Figure 5a). The thickness of ZrO<sub>2</sub> film for gate dielectrics was 10 nm. Oxygen treatment was also employed for the device fabrication.

Figure 5 panels a, b, and c show the transfer characteristics of 15, 45, and 65 nm  $L_{\rm G}$  devices with multiple nanotube channels, respectively. The  $I_{\rm ON}/I_{\rm OFF}$  ratio for the 15 nm  $L_{\rm G}$  device is larger than 10<sup>4</sup> at  $V_{\rm D} = -0.1$  V and larger than 10<sup>3</sup> at  $V_{\rm D} = -0.5$  V. Moreover, the

Figure 5. Representative transfer characteristics of the devices with multiple SWNT channels at different  $V_D$  (-0.1 V, -0.3 V, and -0.5 V) for (a) 15 nm, (b) 45 nm, and (c) 65 nm devices. Inset in frame a: AFM of a test structure (z-scale is 30 nm) to extract the number of nanotubes inside the channel. The estimated number of nanotubes inside the channel is 3-4. (d) Output characteristics of the 15 nm  $L_G$  device. The gate overdrive voltage was increased from 0 to 1.5 V in 0.5 V step.

transconductance of the 15 nm  $L_{G}$  device is up to 73  $\mu$ S. These large  $I_{ON}/I_{OFF}$  ratio and excellent transconductance suggest that the devices with multiple solutionprocessed nanotube channels are also effectively controlled by the combination of a top-gate structure and high- $\kappa$  gate insulators. The 15 nm  $L_{G}$  device also shows current saturation around  $V_{\rm D} = -0.35$  V at  $|V_{\rm G} - V_{\rm T}| =$ 1.5 V in the on-state (Figure 5d). However, there is a slight increase in the minimum current as L<sub>G</sub> decreases, primarily a result of back-injection of carriers into the conduction band from the drain. In addition, the slightly increased subthreshold values and  $V_{T}$  roll-up for decreasing L<sub>G</sub>, indicating mild short-channel effects, are attributed to the somewhat thick gate dielectric layer and may be addressed by using thinner EOT. Note that the I<sub>ON</sub> levels for the two set of devices that have  $L_{\rm G} \leq 45$  nm are almost consistent ( $\langle I_{\rm ON} \rangle$  = 60  $\mu$ A for 15 nm  $L_{\rm G}$  devices,  $\langle I_{\rm ON} \rangle$  = 61  $\mu$ A for 45 nm  $L_{\rm G}$ devices, and  $\langle I_{\rm ON} \rangle$  = 36  $\mu$ A for 65 nm  $L_{\rm G}$  devices at  $|V_{\rm G} - V_{\rm T}| = 1.5$  V) in the same manner as the results of single nanotube channel devices.

## SUMMARY

We evaluated the performance of short-channel, top-gate, solution-processed carbon nanotube devices with high- $\kappa$  gate dielectrics. Electrical characterization of the device indicates that the structural defects in the solution-processed nanotubes, which might result from the purification or suspension processes and can act as localized electron-scattering centers, limit the electron transport characteristics; however, they do not significantly affect the quality of the contact between the nanotubes and metal electrodes. Moreover, we found that the oxygen treatment can effectively decrease the contact resistances. Therefore, measurements of the 15 nm  $L_{\rm G}$  devices with a single solutionprocessed nanotube showed a transconductance of 32  $\mu$ S and a high  $I_{\rm ON}/I_{\rm OFF}$ . These values are comparable to those previously reported for CVD nanotubes and demonstrate the potential of solution-processed nanotubes for future nanoelectronics. Moreover, the further aggressive scaling down to 15 nm  $L_{\rm G}$  for the multiple nanotube channel devices reaches a transconductance of 73  $\mu$ S with a reasonable  $I_{\rm ON}/I_{\rm OFF}$  ratio. Further progress will follow improvement in the purity and placement of the solution-processed nanotubes and the optimization of the transistor structure and integration.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was supported by the MSD Focus Center, one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity and DARPA/DSO Maximum Mobility and Manipulation.

## **REFERENCES AND NOTES**

- 1. Avouris, P.; Chen, Z.; Perebeinos, V. Carbon-Based Electronics. *Nat. Nanotechnol.* **2007**, *2*, 605–615.

- Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; Mcintyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. High-κ Dielectrics for Advanced Carbon-Nanotube Transistors and Logic Gates. *Nat. Mater.* **2002**, *1*, 241–246.

- Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. Ballistic Carbon Nanotube Field-Effect Transistors. *Nature* 2003, 424, 654–657.

- Javey, A.; Guo, J.; Farmer, D. B.; Wang, Q.; Wang, D.; Gordon, R. G.; Lundstrom, M.; Dai, H. Carbon Nanotube Field-Effect Transistors with Integrated Ohmic Contacts and High-κ Gate Dielectrics. *Nano Lett.* **2004**, *4*, 447–450.

- Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V.; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nat. Nanotechnol.* 2007, 2, 230–236.

- Zhou, X.; Park, J.-Y.; Huang, S.; Liu, J.; McEuen, P. Band Structure, Phonon Scattering, and Performance Limit of Single-Walled Carbon Nanotube Transistors. *Phys. Rev. Lett.* 2005, 95, 146805.

- Mann, D.; Javey, A.; Kong, J.; Wang, Q.; Dai, H. Ballistic Transport in Metallic Nanotubes with Reliable Pd Ohmic Contacts. *Nano Lett.* **2003**, *3*, 1541–1544.

- Collins, P. G.; Arnold, M. S.; Avouris, P. Engineering Carbon Nanotubes and Nanotube Circuits Using Electrical Breakdown. *Science* 2001, 292, 706–709.

- Arnold, M. S.; Green, A. A.; Hulvat, J. F. Sorting Carbon Nanotubes by Electronic Structure Using Density Differentiation. *Nat. Nanotechnol.* 2006, 1, 60–65.

- Green, A. A.; Hersam, M. C. Nearly Single-Chirality Single-Walled Carbon Nanotubes Produced *via* Orthogonal Iterative Density Gradient Ultracentrifugation. *Adv. Mater.* 2011, 23, 2185–2190.

- Tu, X.; Manohar, S.; Jagota, A.; Zheng, M. DNA Sequence Motifs for Structure-Specific Recognition and Separation of Carbon Nanotubes. *Nature* 2009, 460, 250–253.

- Moshammer, K.; Hennrich, F.; Kappes, M. M. Selective Suspension in Aqueous Sodium Dodecyl Sulfate According to Electronic Structure Type Allows Simple Separation of Metallic from Semiconducting Single-Walled Carbon Nanotubes. *Nano Res.* 2009, 2, 599–606.

- Liu, H.; Nishide, D.; Tanaka, T.; Kataura, H. Large-Scale Single-Chirality Separation of Single-Wall Carbon Nanotubes

by Simple Gel Chromatography. *Nat. Commun.* **2011**, *2*, 1–8.

- Engel, M.; Small, J. P.; Steiner, M.; Freitag, M.; Green, A. A.; Hersam, M. C.; Avouris, P. Thin-Film Nanotube Transistors Based on Self-Assembled, Aligned, Semiconducting Carbon Nanotube Arrays. ACS Nano 2008, 2, 2445–2152.

- LeMieux, M. C.; Roberts, M.; Barman, S.; Jin, Y. W.; Kim, J. M.; Bao, Z. Self-Sorted, Aligned Nanotube Networks for Thin-Film Transistors. *Science* **2008**, *321*, 101–104.

- Wang, W.; LeMieux, M.; Selvarasah, S. Dip-Pen Nanolithography of Electrical Contacts to Single-Walled Carbon Nanotubes. ACS Nano 2009, 3, 3543–3551.

- Kim, W.-J.; Lee, C. Y.; O'brien, K.; Plombon, J. J.; Blackwell, J. M.; Strano, M. S. Connecting Single Molecule Electrical Measurements to Ensemble Spectroscopic Properties for Quantification of Single-Walled Carbon Nanotube Separation. J. Am. Chem. Soc. 2009, 242, 3128–3129.

- Wang, C.; Zhang, J.; Ryu, K.; Badmaev, A.; De Arco, L. G.; Zhou, C. Wafer-Scale Fabrication of Separated Carbon Nanotube Thin-Film Transistors for Display Applications. *Nano Lett.* **2009**, *9*, 4285–4291.

- Stokes, P.; Khondaker, S. I. High Quality Solution Processed Carbon Nanotube Transistors Assembled by Dielectrophoresis. *Appl. Phys. Lett.* **2010**, *96*, 083110.

- Cao, Q.; Han, S.-J.; Tulevski, G. S.; Franklin, A. D.; Haensch, W. Evaluation of Field-Effect Mobility and Contact Resistance of Transistors That Use Solution-Processed Single-Walled Carbon Nanotubes. ACS Nano 2012, 6, 6471– 6477.

- Sharma, R.; Lee, C. Y.; Choi, J. H.; Chen, K.; Strano, M. S. Nanometer Positioning, Parallel Alignment, and Placement of Single Anisotropic Nanoparticles Using Hydrodynamic Forces in Cylindrical Droplets. *Nano Lett.* 2007, *7*, 2693–2700.

- Duggal, R.; Hussain, F.; Pasquali, M. Self-Assembly of Single-Walled Carbon Nanotubes into a Sheet by Drop Drying. *Adv. Mater.* 2006, *18*, 29–34.

- LeMieux, M. C.; Sok, S.; Roberts, M. E.; Opatkiewicz, J. P.; Liu, D.; Barman, S. N.; Patil, N.; Mitra, S.; Bao, Z. Solution Assembly of Organized Carbon Nanotube Networks for Thin-Film Transistors. ACS Nano 2009, 3, 4089–4097.

- Takei, K.; Madsen, M.; Fang, H.; Kapadia, R.; Chuang, S.; Kim, H. S.; Liu, C.-H.; Plis, E.; Nah, J.; Krishna, S.; Chueh, Y.-L.; Guo, J.; Javey, A. Nanoscale InGaSb Heterostructure Membranes on Si Substrates for High Hole Mobility Transistors. *Nano Lett.* **2012**, *12*, 2060–2066.

- Javey, A.; Guo, J.; Farmer, D. B.; Wang, Q.; Yenilmez, E.; Gordon, R. G.; Lundstrom, M.; Dai, H. Self-Aligned Ballistic Molecular Transistors and Electrically Parallel Nanotube Arrays. *Nano Lett.* **2004**, *4*, 1319–1322.

- Raychowdhury, A.; De, V. K.; Kurtin, J.; Borkar, S. Y.; Roy, K.; Keshavarzi, A. Variation Tolerance in a Multichannel Carbon-Nanotube Transistor for High-Speed Digital Circuits. *IEEE Trans. Electron Devices* **2009**, *56*, 383–392.

- Franklin, A. D.; Lin, A.; Philip Wong, H.-S.; Chen, Z. Current Scaling in Aligned Carbon Nanotube Array Transistors with Local Bottom Gating. *IEEE Electron Device Lett.* 2010, 31, 644–646.

- Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, P. Controlling Doping and Carrier Injection in Carbon Nanotube Transistors. *Appl. Phys. Lett.* **2002**, *80*, 2773–2775.

- Pan, Y.; Huijsing, H. New Method for the Extraction of MOSFET Parameters. *Electron. Lett.* **1988**, *24*, 543–545.

- Franklin, A. D.; Chen, Z. Length Scaling of Carbon Nanotube Transistors. *Nat. Nanotechnol.* 2010, *5*, 858–862.

- Ho, X.; Ye, L.; Rotkin, S. V.; Cao, Q.; Unarunotai, S.; Salamat, S.; Alam, M. A.; Rogers, J. A. Scaling Properties in Transistors That Use Aligned Arrays of Single-Walled Carbon Nanotubes. *Nano Lett.* **2010**, *10*, 499–503.

- Franklin, A. D.; Luisier, M.; Han, S.-J.; Tulevski, G. T.; Breslin, C. M.; Gignac, L.; Lundstrom, M.; Haensch, W. Sub-10 nm Carbon Nanotube Transistor. *Nano Lett.* **2012**, *12*, 758– 462.

- Wu, J.; Xie, L.; Hong, G.; Lim, H. E.; Thendie, B.; Miyata, Y.; Shinohara, H.; Dai, H. Short Channel Field-Effect Transistors

from Highly Enriched Semiconducting Carbon Nanotubes. *Nano Res.* **2012**, *5*, 388–394.