# ARTICLE

# Parallel Array InAs Nanowire Transistors for Mechanically Bendable, Ultrahigh Frequency Electronics

Toshitake Takahashi,<sup>†,‡,§,⊥</sup> Kuniharu Takei,<sup>†,‡,§,⊥</sup> Ehsan Adabi,<sup>†</sup> Zhiyong Fan,<sup>†,‡,§</sup> Ali M. Niknejad,<sup>†</sup> and Ali Javey<sup>†,‡,§,</sup>\*

<sup>†</sup>Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, <sup>‡</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, and <sup>§</sup>Berkeley Sensor and Actuator Center, University of California, Berkeley, California 94720. <sup>⊥</sup>These authors contributed equally to this work.

ver the past several years, semiconductor nanowires (NWs) have been extensively explored for electronic and sensor applications<sup>1-8</sup> owing to their unique physical properties with tunable and well-defined atomic composition.9 In one specific platform, a contact printing technique is utilized for the largescale assembly of NW parallel arrays on a support substrate, followed by the subseguent device fabrication.<sup>10–13</sup> Since NW arrays are utilized, the stochastic device-todevice variation is drastically reduced, which is of practical importance.<sup>14–16</sup> The performance limits of the enabled devices, however, are still unknown. In this regard, here we characterize the radio frequency (RF) response of InAs NW array transistors on bendable substrates, elucidating an important performance metric for determining their potential application domain. Notably, for the first time, the GHz operation of mechanically flexible, NW parallel array devices is demonstrated. The results demonstrate the potential of NW array devices for ultrahigh frequency (UHF) electronic circuits.

UHF electronics operating in the 0.3–3 GHz regime are highly attractive for various analog and digital circuits.<sup>17,18</sup> The ability to fabricate these devices on mechanically bendable substrates that conform nonplanar surfaces and potentially by printing techniques may further broaden their utility and application domain. In this work, highly aligned InAs NW arrays were utilized as the active channel material of the flexible, UHF field-effect transistors (FETs). InAs NWs are attractive for such applications due to their high electron mobility,<sup>2,4,19</sup> high electron saturation velocity, ease of ohmic **ABSTRACT** The radio frequency response of InAs nanowire array transistors on mechanically flexible substrates is characterized. For the first time, GHz device operation of nanowire arrays is demonstrated, despite the relatively long channel lengths of  $\sim$ 1.5 µLm used in this work. Specifically, the transistors exhibit an impressive maximum frequency of oscillation,  $f_{max} \sim$  1.8 GHz, and a cutoff frequency,  $f_t \sim$  1 GHz. The high-frequency response of the devices is due to the high saturation velocity of electrons in high-mobility InAs nanowires. The work presents a new platform for flexible, ultrahigh frequency devices with potential applications in high-performance digital and analog circuitry.

**KEYWORDS:** nanowires  $\cdot$  flexible electronics  $\cdot$  printed  $\cdot$  plastic  $\cdot$  radio frequency devices

metal contact formation,<sup>4,20</sup> and miniaturized diameters that make them mechanically flexible.

InAs NWs used in this study were synthesized on Si/SiO<sub>2</sub> substrates by a physical vapor transport method.<sup>4</sup> The grown NWs had an average diameter and length of  $\sim$  30 nm and  $\sim$ 10  $\mu$ m. Subsequently, NW contact printing<sup>10,11,15</sup> was carried out by directionally sliding a growth substrate, consisting of randomly grown InAs NWs, on top of a polyimide (PI) layer (24 µm) spin-coated on a Si/SiO<sub>2</sub> handling wafer. During this process, NWs are directly transferred from the growth substrate to the PI surface as parallel arrays.<sup>10,11,15</sup> To achieve patterned assembly of NWs, the PI surface is first coated with a lithographically patterned resist layer, followed by NW printing and lift-off in a solvent. Nickel ( $\sim$ 50 nm) source (S) and drain (D) electrodes were then formed, followed by atomic layer deposition of Al<sub>2</sub>O<sub>3</sub>  $(\sim 8 \text{ nm})$  at 150 °C as the gate dielectric. Finally, AI (40 nm) top-gate (G) electrodes were fabricated. All electrodes were defined by photolithography and lift-off processes. There is  $\sim$ 200 nm of misalignment due to the limitation of contact aligner,

\*Address correspondence to ajavey@berkeley.edu.

Received for review July 29, 2010 and accepted September 08, 2010.

Published online September 16, 2010. 10.1021/nn1018329

© 2010 American Chemical Society

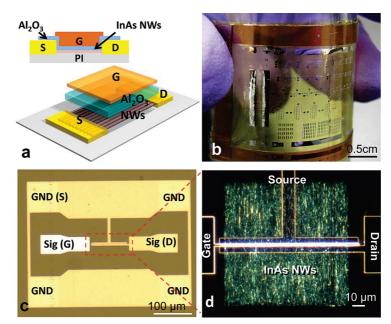

Figure 1. Schematic and optical images of a printed InAs NW array FET fabricated on a flexible PI substrate for GHz operation. (a) Schematic illustration of the NW parallel array FET, illustrating the various layers of the device. The cross-sectional image is shown in the top. (b) Photograph image of the fabricated NW device array on a bendable PI substrate. (c) Brightfield optical image of a NW array FET with ground-signal-ground configuration for the RF measurements. (d) Dark-field optical image, showing the printed InAs NW region.

resulting in the overlap of G with one of the S/D electrodes and underlap with the other, resulting in a parasitic capacitance and series resistance, respectively. The channel length (S/D electrode spacing) is  $L \sim 1.5$  $\mu$ m, and the channel width is  $W = 100-200 \mu$ m. The gate electrode length is  $L_{\rm G} \sim 1.4 \,\mu$ m. The configuration of the electrical pads matches that of the conventional ground-signal-ground (GSG) microwave probes (150 µm pitch). Figure 1a shows the layered schematic of a NW array RF device. The optical microscopy images of a completed device are shown in Figure 1c,d, clearly depicting the active NW array region and the GSG electrode configuration. The printed NW density is  $\sim$ 4 NWs/µm as confirmed by scanning electron microscopy. After the completion of the fabrication process, the PI layer is peeled off from the rigid Si/SiO<sub>2</sub> handling wafer, resulting in mechanically flexible device arrays, as shown in Figure 1b.

Figure 2a shows representative output characteristics of an InAs NW array FET with  $W = 100 \ \mu\text{m}$  on a flexible PI substrate. The FET delivers a unit-width normalized ON current of  $I_{ON} \sim 23 \ \mu\text{A}/\mu\text{m}$  at  $V_{DS} = 2 \ V$ . Individual NWs with comparable lengths and diameters deliver ~10  $\mu$ A of ON current based on our previous studies.<sup>4</sup> From the current density, we estimate that ~2 NW/ $\mu$ m cross the S/D electrodes, with the rest of the NWs only contacting one electrode and thereby serving as parasitic elements (*i.e.*, they contribute to the gate capacitance but not the transconductance). A respectable ON/OFF current ratio,  $I_{ON}/I_{OFF} \sim 100$  is observed at  $V_{DS} = 2.5 \ V$ , as shown in the inset of Figure 2b. From the  $I_{DS}-V_{GS}$  curve at  $V_{DS} = 2.5 \ V$ , the peak transconductance,  $g_m = (dI_{DS}/dV_{GS})|_{V_{DS}} \sim 1.1 \ ms$  (*i.e.*, ~11  $\mu$ S/ $\mu$ m as normalized by *W*) is measured at  $V_{GS} = -0.5$  V (Figure 2b). From the slope of  $I_{DS} - V_{DS}$  curve at  $V_{DS} = 2.5$  V and  $V_{GS} = -0.4$  V, the output resistance,  $r_o \sim 8 \ k\Omega$  is obtained, which corresponds to a gain of  $A_v = r_o g_m \sim 8$ .  $A_v$  is the intrinsic gain of a transistor with no loading (*i.e.*, transistor is self-loaded), which is an important figure for operation amplifiers, instrumentation amplifiers, and other circuit components where large gains are desirable. Furthermore, the mechanical flex-

Figure 2. DC characteristics of an InAs NW array FET. (a) Normalized output characteristics of a NW array FET with a channel width,  $W \sim 100 \mu$ m, and gate length,  $L_{\rm G} \sim 1.5 \mu$ m. (b) Linear-scale transfer characteristic and the corresponding transconductance as a function of gate bias at  $V_{\rm DS} = 2.5$ V. The log-scale  $I_{\rm DS}-V_{\rm GS}$  at  $V_{\rm DS} = 2.5$  V is shown in the inset.

5856

SNANO

ARTICLE

ibility of the devices was tested by measuring the electrical properties as a function of the radius of curvature. The NW array FETs do not exhibit a significant electrical degradation, even when bent to a radius of ~18 mm with compressive/tensile stress (see Supporting Information, Figure S1), which is attributed to the miniaturized dimensions of NWs. Additionally, since InAs NWs have significantly higher Young's modulus than the supporting PI substrate, the strain is mostly compensated by the substrate, with the strain in the NW being only  $\varepsilon_{xx} \sim 0.5\%$ , as predicted from mechanical simulations (Figure S1b).

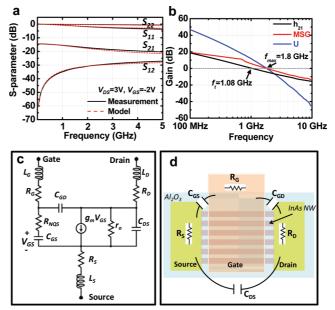

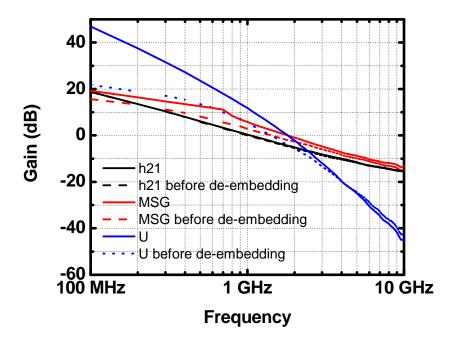

To directly extract the high-frequency behavior, the two-port scattering parameters (S parameters) of InAs NW array FETs were measured in the common-source configuration using standard procedures with a vector network analyzer (VNA) over a frequency range from 40 MHz to 10 GHz (Anritsu 37397C). Calibration of the probe tips was performed by employing the shortopen-load-thru method (see Supporting Information) on an impedance standard substrate provided by Cascade Microtech (ISS 101-190). On-wafer pad-open and pad-short structures (Figure S2) were used to de-embed the parasitic effects of the contact pads, that is, shunt capacitance/conductance and series inductance/resistance (see Supporting Information for the details). This de-embedding does not correct for the overlap capacitances between the gate and source/drain electrodes. The S parameters were then used to analyze the RF performance of the device (Figure 3a). S<sub>11</sub>, S<sub>22</sub>, S<sub>21</sub>, and S<sub>12</sub> are, respectively, the reflection coefficient of the input, the reflection coefficient of the output, the forward transmission gain, and the reverse transmission gain. Figure 3b shows various RF metrics of a representative device with  $W = 200 \,\mu$ m, all derived from S parameters. Specifically, unity transit frequency of the current gain  $(h_{21})$  of a transistor is called  $f_t$  and is an important factor for determining the high-frequency limit of the transistor for various analog/RF and digital applications. To obtain  $f_t$  from the measurements, S parameters are first converted to hybrid parameters (h parameters) as described in the Supporting Information. The parameter  $h_{21}$  is plotted as a function of frequency (Figure 3b), and  $f_t$  occurs at the frequency where  $h_{21}$  equals 1, that is, 0 dB. As depicted in Figure 3b, InAs NW array FETs exhibit an impressive  $f_t = 1.08$  GHz. Maximum stable gain (MSG), the gain a transistor can provide if suitable input and output matching networks are incorporated for an unconditionally stable amplifier design, is also extracted (see Supporting Information) and plotted as a function of frequency (Figure 3b). At 1 GHz, the MSG of the FET is  $\sim$ 6 dB, which confirms that designing an RF amplifier at the GHz regime is plausible. Finally, maximum unilateral gain (U, Mason gain) is extracted (Supporting Information) as a function of frequency (Figure 3b). Mason gain is the maximum unilateral power gain the device can provide at a specific frequency of opera-

Figure 3. RF characterization of an InAs NW array FET. (a) Measured (black solid line) and modeled (red dashed line) scattering parameters,  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$ , and  $S_{22}$  of an InAs NW array FET with  $W \sim 200 \,\mu$ m after de-embedding for frequencies between 40 MHz and 5 GHz. (b) Current gain ( $h_{21}$ ), maximum stable gain (MSG), and unilateral power gain (U) extracted from measured S parameters as a function of frequency. The unity current gain frequency,  $t_{tr}$  and unity power gain frequency,  $f_{maxr}$  are  $\sim 1.08$  and 1.8 GHz, respectively. (c) Small signal equivalent circuit model and (d) device schematic, illustrating the various circuit components.  $R_5$ ,  $R_0$ , and  $R_6$  are composed of metal sheet resistance and contact resistance.

tion. The maximum frequency of oscillation,  $f_{max}$ , is determined by extracting Mason's gain at 0 dB. It is an important figure of merit, and at frequencies beyond  $f_{max}$ , a transistor cannot provide any power gain and turns into a passive component. As shown in Figure 3b, the NW array FET has  $f_{max} = 1.8$  GHz.

A small signal model can also be fitted to the *S* parameter data to be used in the future circuit design and optimizations and further extract key device parameters. The small signal equivalent circuit is shown in Figure 3c,d. At the core is the hybrid- $\pi$  model of the transistor including  $g_m$ ,  $r_o$ , and the capacitances ( $C_{GS}$ ,  $C_{GD}$ , and  $C_{DS}$ ). Non-quasi-static (NQS) resistance,  $R_{NQS}$ , and the series resistance ( $R_G$ ,  $R_S$ ,  $R_D$ ) and inductance ( $I_G$ ,  $I_S$ ,  $I_D$ ) associated with the gate, source, and drain interconnects are added, resulting in the match between measured data and the fitted small signal model data (Figure 3a; see Supporting Information for details). The extracted component values for the small signal model are listed in Table 1.

To further characterize the devices, *S* parameters were measured at different drain and gate voltages with the extracted  $f_t$  shown in Figure 4a. As expected,  $f_t$  monotonically increases with  $V_{DS}$  for the explored bias range due to an increase in  $g_m$ . The peak  $f_t$  is obtained at  $V_{GS} = -2$  V, most likely corresponding to when the Fermi level coincides with the first conduction sub-band edge of the InAs NW channel. Due to the

www.acsnano.org

VOL. 4 • NO. 10 • 5855-5860 • 2010

2.3 mS

13 k $\Omega$

315 fF

| TABLE 1. Extracted and Fitted Parameters from Small Signal RF Modeling for a NW Array FET with W = 200 $\mu$ m and L = |                |                 |     |     |    |    |    |      |                |   |                |

|------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----|-----|----|----|----|------|----------------|---|----------------|

| 1.5 μm                                                                                                                 |                |                 |     |     |    |    |    |      |                |   |                |

| q <sub>m</sub>                                                                                                         | r <sub>o</sub> | ( <sub>65</sub> | CGD | Cos | Ro | Rs | Rp | RNOS | I <sub>6</sub> | k | I <sub>n</sub> |

66 $\Omega$

73 Ω

85 Ω

200 pH

92 pH

148 pH

102  $\Omega$

nonparabolicity of the band structure, effective mass increases as the Fermi level goes deeper into the conduction band, thereby lowering the electron mobility and saturation velocity. Since cutoff frequency is proportional to saturation velocity, it follows that as higher positive gate voltages,  $f_t$  decreases. Similarly,  $g_m$  can be extracted as a function of bias from the RF measurements (Figure 4b). A peak transconductance of  $g_m \sim 12 \,\mu\text{S}/\mu\text{m}$  at  $V_{\text{DS}} = 3 \,\text{V}$  and  $V_{\text{GS}} = -2 \,\text{V}$  is obtained from the AC small signal RF characteristics, which is consistent with the value obtained from the DC measurements (Figure 2b). Note that the devices in Figures 2 and 4 are not the same. Due to the device-to-device variations, the threshold voltage is slightly different.

35 fF

10 fF

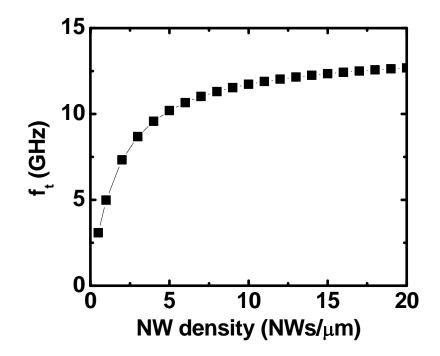

Next, we examine the theoretical performance limit of InAs NW array FETs. The cutoff frequency is projected from the relation,  $f_t = g_m/(2\pi(C_{GS} + C_{GD}))$ . In the high field operation regime (e.g., high  $V_{DS}$  and/or short  $L_G$ , as is the case in this work), the carriers propagate at the saturation velocity,  $v_{satr}$  with the transconductance given as  $g_m = v_{sat}(C_{ox}/L_G)$ . Here  $C_{ox}$  is the gate oxide capacitance and can be obtained from  $C_{ox} = C_{ox,1} \times (Wd)$ , where  $C_{ox,1}$  is the NW gate capacitance for a single NW and d is the NW density. The cutoff frequency is then  $f_t$  $= v_{sat}C_{ox}/(2\pi L_G(C_{GS} + C_{GD}))$ . Note that the total gate source capacitance is given as  $C_{GS} = C_{p,GS} + 2/3C_{oxr}$ where  $C_{p,GS}$  is the parasitic capacitance between G/S electrodes. The exact velocity-field curve for InAs NWs

Figure 4. Bias dependence of the RF response. (a,b) Measured unity current gain frequency and transconductance as a function of  $V_{GS}$  and  $V_{DS}$  for a NW array FET with  $W = 200 \mu$ m.

is unknown, so we use the bulk curve for the purpose of this analysis. The cutoff frequency is then calculated by using the extracted capacitances for the explored device geometry (Table 1) and  $v_{\rm sat}$   $\sim$  1.3 imes 10<sup>7</sup> cm/s at a field of 16 kV/cm (corresponding to  $V_{\rm DS} = 2.5$  V and  $L_{\rm G}$ = 1.5  $\mu$ m).<sup>21</sup> From this analysis,  $f_{\rm t}$  ~ 7 GHz is projected for d = 2 NWs/µm (Figure S4, Supporting Information) and  $L_q = 1.5 \ \mu$ m, which is  $\sim$ 7 times higher than the experimental  $f_t$  for the same NW density. This may be attributed to the dominant rote of surface scattering in the electron transport properties of unoptimized InAs NWs used in this work. In the future, exploration of surface passivation layers may help to further enhance the measured frequency response of NW RF-FETs. Additionally, by increasing the printed NW density to 20 NWs/ $\mu$ m (50 nm pitch), the theoretical  $f_t$  increases to  $\sim$ 13 GHz. Finally, in the absence of all parasitic elements, an ultimate theoretical  $f_t$  of  $\sim$ 14 GHz is projected, presenting the "intrinsic" cutoff frequency of the InAs transistors at the explored length scales. Further gate length miniaturization can also enhance the RF performance.

The GHz operation of our FETs compares favorably with the other previously explored flexible device concepts. For example, hydrogen-terminated amorphous silicon or silicon films with various degrees of crystallinity have been widely utilized for applications in largescale electronics with the highest reported  $f_t$  of  $\sim$ 250 MHz on plastic substrates.<sup>22</sup> Organic transistors have been limited to  $f_t$  of ~10 MHz<sup>23</sup> due to their low carrier mobilities. Several groups have achieved GHz operation using carbon nanotube arrays on either a plastic or rigid substrate<sup>17,24-27</sup> and graphene on a rigid substrate.<sup>28</sup> However, these devices exhibit poor  $I_{ON}$ /  $I_{OFF}$  due to the mixture of metallic nanotubes in the arrays and the small band gap of graphene. Previous work utilizing NWs for flexible electronics resulted in devices operating at 10-100 MHz,<sup>29-31</sup> although higher frequencies have been reported for single NWs with short channels on rigid Si substrates.<sup>32</sup> Egard et al.<sup>33</sup> recently reported GHz devices with  $f_t > 7$  GHz and  $f_{max} > 20$  GHz based on vertical InAs NW arrays grown epitaxially on InP wafers with a gate length of  $\sim$ 100 nm. This works shows the potential of InAs NWs for high-frequency transistors; however, the explored structure and geometry are not compatible with flexible electronics. Recently, promising flexible devices<sup>34</sup> are reported using inorganic single-crystalline flakes such as Si ( $f_{\rm t} \sim 0.5 - 3$ GHz for  $L_{\rm G}$   $\sim$  2  $\mu$ m)<sup>35,36</sup> and GaAs ( $f_{\rm t}$   $\sim$  1.5 GHz for  $L_{\rm G}$   $\sim$ 2 µm).<sup>37</sup> These devices are fabricated via top-down etching and subsequent transfer method. The RF NW

5858

device concept presented here has the advantage of potentially utilizing an all-printed fabrication scheme, without the need for complex lithographic processes.

The presented results show the potential of NW array FETs for future microwave applications on nonconventional substrates as enabled by (i) the uniform and dense assembly of NW parallel arrays, (ii) the inherently high saturation velocity of InAs, and (iii) the appropriate device design. This technology is of particular interest given the recent rapid growth of signal communication over the UHF bands. Notably, the explored device dimensions are within the resolution limit of advanced printing processes,<sup>38</sup> thereby making the presented platform potentially compatible with continuous rollto-roll fabrication processes. In the future, further miniaturization of the device dimensions, improved printed NW array densities, and the use of surface passivation layers through process optimization are projected to enhance the cutoff frequency of the devices by an additional ~10-fold. This projected performance cap is comparable to that of the state-of-the-art nanoscale Si devices but uniquely is attainable on nonrigid substrates and with all-printed fabrication processes.

Acknowledgment. This work was partially funded by MARCO/ MSD Focus Center Research Program, Berkeley Sensors and Actuator Center, and NSF CAREER Award. The synthesis part of this work was supported by a LDRD from Lawrence Berkeley National Laboratory. A.J. acknowledges a support from the World Class University program at Sunchon National University. We acknowledge Paul Leu for help with the mechanical simulations.

Supporting Information Available: Mechanical bendability of NW array FETs; details of de-embedding pad parasitic; extraction of  $h_{21}$ , MSG, and U from the S parameters; hybrid- $\pi$  model; the effect of NW density on extrinsic cutoff frequency. This material is available free of charge *via* the Internet at http:// pubs.acs.org.

### **REFERENCES AND NOTES**

- Xiang, J.; Lu, W.; Hu, Y.; Wu, Y.; Yan, H.; Lieber, C. M. Ge/Si Nanowire Heterostructures as High-Performance Field-Effect Transistors. *Nature* 2006, 441, 489–493.

- Bryllert, T.; Wernersson, L. E.; Froberg, L. E.; Samuelson, L. Vertical High-Mobility Wrap-Gated InAs nanowire Transistor. *IEEE Electron Device Lett.* 2006, *27*, 323–325.

- Wang, D.; Sheriff, B.; Heath, J. R. Complementary Symmetry Silicon Nanowire Logic: Power-Efficient Inverters with Gain. Small 2006, 2, 1153–1158.

- Ford, A. C.; Ho, J. C.; Chueh, Y.-L.; Tseng, Y.-C.; Fan, Z; Guo, J.; Bokor, J.; Javey, A. Diameter-Dependent Electron Mobility of InAs Nanowires. *Nano Lett.* **2009**, *9*, 360–365.

- Ju, S.; Facchetti, A.; Xuan, Y.; Liu, J.; Ishikawa, F.; Ye, P.; Zhou, C.; Marks, T. J.; Jane, D. B. Fabrication of Fully Transparent Nanowire Transistors for Transparent and Flexible Electronics. *Nat. Nanotechnol.* 2007, *2*, 378–384.

- 6. Ju, S.; *et al.* Transparent Active Matrix Organic Light-Emitting Diode Displays Driven by Nanowire Transistor Circuitry. *Nano Lett.* **2008**, *8*, 997–1004.

- Stern, E.; Klemic, J. F.; Routenberg, D. A.; Wyrembak, P. N.; Turner-Evans, D. B.; Hamilton, A. D.; LaVan, D. A.; Fahmy, T. M.; Reed, M. A. Label-Free Immunodetection with CMOS-Compatible Semiconducting Nanowires. *Nature* 2007, 445, 519–522.

- 8. Cohen-Karni, T.; Timko, B. P.; Weiss, L. E.; Lieber, C. M.

Flexible Electrical Recording from Cells Using Nanowire Transistor Arrays. *Proc. Natl. Acad. Sci. U.S.A.* **2009**, *106*, 7309–7313.

- Lieber, C. M.; Wang, Z. L. Functional Nanowires. *MRS Bull.* 2007, 32, 99.

- Yerushalmi, R.; Jacobson, Z. A.; Ho, J. C.; Fan, Z.; Javey, A. Large Scale, Highly Ordered Assembly of Nanowire Parallel Arrays by Differential Roll Printing. *Appl. Phys. Lett.* 2007, *91*, 203104.

- Fan, Z.; Ho, J. C.; Jacobson, Z. A.; Yerushalmi, R.; Alley, R. L.; Razavi, H.; Javey, A. Wafer-Scale Assembly of Highly Ordered Semiconductor Nanowire Arrays by Contact Printing. *Nano Lett.* **2008**, *8*, 20–25.

- Takahashi, T.; Takei, K.; Ho, J. C.; Chueh, Y.-L.; Fan, Z.; Javey, A. Monolayer Resist for Patterned Contact Printing of Aligned Nanowire Arrays. J. Am. Chem. Soc. 2009, 131, 2102–2103.

- Fan, Z.; Ho, J. C.; Takahashi, T.; Yerushalmi, R.; Takei, K.; Ford, A. C.; Chueh, Y.-L.; Javey, A. Towards the Development of Printable Nanowire Electronics and Sensors. *Adv. Mater.* 2009, *21*, 3730–3743.

- Javey, A.; Nam, S.; Friedman, R. S.; Yan, H.; Lieber, C. M. Layer-by-Layer Assembly of Nanowires for Three-Dimensional, Multifunctional Electronics. *Nano Lett.* 2007, 7, 773–777.

- Fan, Z.; Ho, J. C.; Jacobson, Z. A.; Razavi, H.; Javey, A. Large Scale, Heterogeneous Integration of Nanowire Arrays for Image Sensor Circuitry. *Proc. Natl. Acad. Sci. U.S.A.* 2008, 105, 11066–11070.

- Takei, K.; Takahashi, T.; Ho, J. C.; Ko, H.; Gillies, A. G.; Leu, P. W.; Fearing, R. S.; Javey, A. Nanowire Active Matrix Circuitry for Low-Voltage Macro-Scale Artificial Skin. *Nat. Mater.* DOI: 10.1038/NMAT2835.

- Rutherglen, C.; Jain, D.; Burke, P. J. Nanotube Electronics for Radiofrequency Applications. *Nat. Nanotechnol.* 2009, 4, 811–819.

- Schwierz, F.; Liou, J. J. RF Transistors: Recent Developments and Roadmap toward Terahertz Applications. *Solid-State Electron*. 2007, *51*, 1079–1091.

- Dayeh, S. A.; Aplin, D. P. R.; Zhou, X.; Yu, P. K. L.; Yu, E. T.; Wang, D. High Electron Mobility InAs Nanowire Field-Effect Transistors. *Small* **2007**, *3*, 326–332.

- Chueh, Y.-L.; Ford, A. C.; Ho, J. C.; Jacobson, Z. A.; Fan, Z.; Chen, C.-Y.; Chou, L.-Y.; Javey, A. Formation and Characterization of Ni<sub>x</sub>InAs/InAs Nanowire Heterostructures by Solid Source Reaction. *Nano Lett.* 2008, *8*, 4528–4533.

- 21. Brennan, K.; Hess, K. High Field Transport in GaAs, InP and InAs. *Solid-State Electron*. **1984**, *27*, 347–357.

- Kane, M. G.; Goodman, L.; Firester, A. H.; van der Wilt, P. C.; Limanov, A. B.; Im, J. S. 100 MHz CMOS Circuits Using Sequential Laterally Solidified Silicon Thin-Film Transistors on Plastic. *Tech Dig. - Int. Electron Devices Meet.* 2005, 939–941.

- 23. Dodabalapur, A. Organic and Polymer Transistors for Electronics. *Mater. Today* **2006**, *9*, 24–30.

- Chimot, N.; Derycke, V.; Goffman, M. F.; Bourgoin, J. P.; Happy, H.; Dambrine, G. Gigahertz Frequency Flexible Carbon Nanotube Transistors. *Appl. Phys. Lett.* **2007**, *91*, 153111.

- Kocabas, C.; *et al.* High-Frequency Performance of Submicrometer Transistors That Use Aligned Arrays of Single-Walled Carbon Nanotubes. *Nano Lett.* 2009, *9*, 1937–1943.

- Close, G. F.; Yasuda, S.; Paul, B.; Fujita, S.; Wong, H.-S. P. A 1 GHz Integrated Circuit with Carbon Nanotube Interconnects and Silicon Transistors. *Nano Lett.* **2008**, *8*, 706–709.

- Rosenblatt, S.; Lin, H.; Sazonova, V.; Tiwari, S.; McEuen, P. L. Mixing at 50 GHz Using a Single-Walled Carbon Nanotube Transistor. *Appl. Phys. Lett.* **2005**, *87*, 153111.

- Lin, Y. M.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.-Y.; Grill, A.; Avouris, P. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. *Science* **2010**, *327*, 622–625.

- Friedman, R. S.; McAlpine, M. C.; Ricketts, D. S.; Ham, D.; Lieber, C. M. High-Speed Integrated Nanowire Circuits. *Nature* 2005, 434, 1085.

- Nam, S. W.; Jiang, X.; Xiong, Q.; Ham, D.; Lieber, C. M. Vertically Integrated, Three-Dimensional Complementary Metal-Oxide-Semiconductor Circuits. *Proc. Natl. Acad. Sci.* U.S.A. 2009, 106, 21035–21038.

- Dattoli, E. N.; Kim, K.-H.; Fung, W. Y.; Choi, S.-Y.; Lu, W. Radio Frequency Operation of Transparent Nanowire Thin-Film Transistors. *IEEE Electron Device Lett.* 2009, 30, 730–732.

- Vandenbrouck, S.; Madjour, K.; Theron, D.; Dong, Y. J.; Li, Y.; Lieber, C. M.; Gaquiere, C. 12 GHz F-MAX GaN/AIN/AIGaN Nanowire MISFET. *IEEE Electron Device Lett.* 2009, 30, 322–324.

- 33. Egard, M.; Johansson, S.; Johansson, A.-C.; Persson, K.-M.; Dey, A. W.; Borg, B. M.; Thelander, C.; Wernersson, L.-E.; Lind, E. Vertical InAs Nanowire Wrap Gate Transistors with  $f_t > 7$  GHz and  $f_{max} > 20$  GHz. *Nano Lett.* **2010**, *10*, 809–812.

- Rogers, J. A.; Huang, Y. A Curvy, Stretchy Future for Electronics. *Proc. Natl. Acad. Sci U.S.A.* 2009, *106*, 10875–10876.

- Ahn, J. H.; Kim, H.-S.; Lee, K. J.; Zhu, Z.; Menard, E.; Nuzzo, R. G.; Rogers, J. A. High-Speed Mechanically Flexible Single-Crystal Silicon Thin-Film Transistors of Plastic Substrates. *IEEE Electron Device Lett.* **2006**, *27*, 460–462.

- Yuan, H.-C.; Ma, Z. Microwave Thin-Film Transistors Using Si Nanomembranes on Flexible Polymer Substrate. *Appl. Phys. Lett.* 2006, 89, 212105.

- Sun, Y.; Menard, E.; Rogers, J. A.; Kim, H.-S.; Kim, S.; Chen, G.; Adesida, I.; Dettmer, R.; Cortez, R.; Tewksbury, A. Gigahertz Operation in Flexible Transistors on Plastic Substrates. *Appl. Phys. Lett.* **2006**, *88*, 183509.

- Park, J.-U.; et al. High-Resolution Electrohydrodynamic Jet Printing. Nat. Mater. 2007, 6, 782–789.

# Parallel Array InAs Nanowire Transistors for Mechanically Bendable, Ultra High Frequency Electronics

Toshitake Takahashi<sup>1,2,3,†</sup>, Kuniharu Takei<sup>1,2,3,†</sup>, Ehsan Adabi<sup>1</sup>, Zhiyong Fan<sup>1,2,3</sup>, Ali M. Niknejad<sup>1</sup> and Ali Javey<sup>1,2,3,\*</sup>

<sup>1</sup>Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA, 94720

<sup>2</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

<sup>3</sup>Berkeley Sensor and Actuator Center, University of California at Berkeley, Berkeley, CA, 94720

<sup>†</sup>These authors contributed equally to this work.

\* Correspondence should be addressed to A.J. (ajavey@berkeley.edu).

# **Supporting Information**

## Mechanical bending of parallel array InAs NW FETs

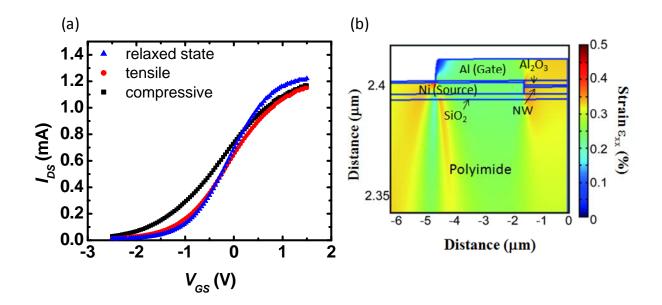

Figure S1: Mechanical bendability of NW-array FETs, Transfer characteristics of an InAs NW-array FET with  $W = 200 \mu m$  measured at  $V_{DS} = 1V$  as a function of the imposed bending condition. The device is first measured at the relaxed state, (bending radius, r = infinity), and under a tensile and compressive strain (r = 18 mm) conditions. **b**, Mechanical simulation of the strain for a NW device when bent to 18 mm curvature radius. Only half of the device is shown, depicting the various layers and their strain.

### Short-open-load-thru (SOLT) calibration method

Electrical cables and probes are used to connect a vector network analyzer (VNA) ports to on-chip pads in order to measure a DUT (device under test). The raw data measured by the VNA is not accurate and contains the added parasitic effects of the cables/connectors and probes at the input and output. To de-embed the effect of these interconnections and calibrate the setup down to probe-tips, firstly a known set of terminations are measured (standard impedance substrate). By measuring these terminations in different configurations, the added parasitic effects of the cable/connectors and probes are obtained and subtracted from the raw measured data and hence the calibrated data, which is only due to the DUT and not the interconnections, is extracted.

### On-wafer pad-open and pad-short for de-embedding pad parasitics

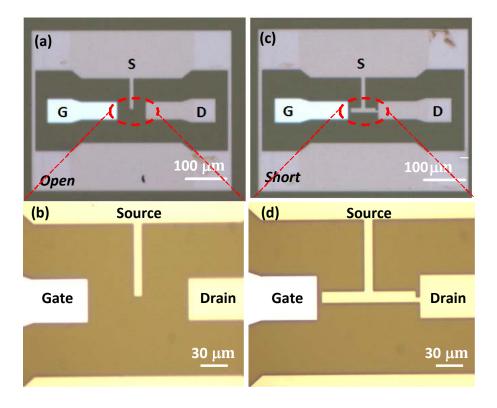

Calibration of the setup through the SOLT procedure (explained above) removes all the off-chip interconnection effects and yields to the measured data of the on-chip structures, which includes input/output pads and the transistor. Since we are only interested in the inherent characteristic of the transistor, the effects of the input/output pads should be removed. One approach is to repeat the SOLT procedure with pad-open, pad-short, pad-loaded, pads-thru structures and de-embed the added parasitic effects of the pads. Since fabricating an accurate and broadband on-chip 50-ohm termination and transmission lines are challenging, and furthermore, since the total structure is small relative to the wavelength of interest, we use a lumped element pad-open and pad-short configurations to de-embed the pad effects (Fig. S2). Pad-open gives the shunt capacitance and its associated conductance of the pad structure, and pad-short gives the series inductance and resistance of the pad/interconnect. Pad-only structures in open and short configurations were placed on the same die. These parasitic effects were then subtracted from the

total pad and transistor structure, and the S-parameters of the intrinsic transistor were obtained. In Figure S3, the measured current gain  $(h_{21})$ , the maximum stable gain (MSG), and maximum unilateral gain (U) before and after de-embedding are shown.

**Figure S2**: (a), (b) Pad-open and (c), (d) pad-short device configurations for de-embedding the pad effects.

**Figure S3**: The effect of de-embedding on the measured current gain  $(h_{21})$ , Maximum stable gain (MSG), and maximum unilateral gain (U).

### Extraction of h<sub>21</sub>, MSG and U from the S-parameters

S-parameters can be converted to h-parameters and hence  $h_{21}$  can be plotted, so  $f_t$  (which is the frequency where  $h_{21}=1=0$  dB) can be directly extracted. Maximum stable gain (MSG) is the theoretical gain a transistor can provide if suitable lossless input and output matching networks are incorporated, and is extracted as following:

$$MSG = (K - \sqrt{K^2 - 1}) \frac{|S_{21}|}{|S_{12}|}$$

for K > 1 (after 700 MHz)

$$MSG = \frac{|S_{21}|}{|S_{12}|}$$

for K < 1 (before 700 MHz)

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{21}S_{12}|}, \Delta = S_{11}S_{22} - S_{12}S_{21}$$

Maximum unilateral gain (U, Mason gain) is the maximum unilateral power gain the device can provide and is calculated from Y or Z (admittance or impedance) parameters as following

$$U = \frac{|Y_{21} - Y_{12}|^2}{4 \times (Re[Y_{11}] \times Re[Y_{22}] - Re[Y_{12}] \times Re[Y_{21}])}$$

The maximum power gain of a device is defined as the power gain delivered by a device when both input and output ports are matched to the impedance of the source and load, respectively. For a MOS device *MSG* is approximately given as:  $MSG \approx \frac{f_t}{8\pi R_G C_{GD} f^2}$  for K > 1. As can be seen from this equation, *MSG* vs frequency, *f*, has a relation of  $MSG \sim 1/f^2$ , or *MSG* drops by 20 dB/decade as frequency increases. In this equation, the frequency effects up to the second order are considered and higher order effects are neglected.

### <u>Hybrid-π model</u>

Transistors are nonlinear devices (nonlinear output  $(i_d)/input (v_g)$  characteristics). To design an amplifier, suitable gate and drain voltages with respect to the source should be applied to the transistor to bias it at a desired operating point. After biasing, we assume the input voltage applied to the gate is small and hence the device can be assumed linear with respect to that. Hence we can derive a small signal linear model of the transistor at that certain bias point and use that for amplifier design. This model is called the hybrid- $\pi$  model of the transistor. At the core there is a voltage controlled current source, which transforms the input voltage to the output current ( $i_2$ =- $g_m.v_1$ ),  $g_m$  being the transconductance of the device. Since the drain current of the transistor (*i*<sub>2</sub>) changes with the drain voltage (*v*<sub>2</sub>), a shunt resistor (*r*<sub>o</sub>) is added to the output (port-2) to emulate that effect. Parasitic capacitances, being present between source/gate/drain terminals, are added to the model through *C*<sub>GD</sub>, *C*<sub>GS</sub>, and *C*<sub>DS</sub>. Series inductance and resistance due to the gate/source and drain interconnects can also be added to the model to make it more accurate. Finally a series non-quasi static (NQS) resistor can be added in series with *C*<sub>GS</sub> to capture the effect of a frequency response. NQS resistance of the channel accounts for the fact that channel charge cannot respond instantaneously to the variation of gate-source voltage. NQS resistance is a distributed effect along the channel length. Electronic carriers (e.g., electrons) at any particular point within the channel of a MOSFET see a resistive element that "points" toward the source and a capacitive element that "points" toward the gate. A direct expression has been obtained for the channel charging resistance  $R_{NQS} = \frac{1}{5g_m}$  in reference [1].

### Calculation of parameters in Table 1

To obtain the small signal model of a transistor, the measured two-port S-parameter data were exploited. The core hybrid- $\pi$  core model of the transistor is realized by calculating impedance and admittance parameters (Z and Y matrixes) and using the following equations:

$g_{\rm m} = -\text{Re}(Y_{21})$   $r_{\rm o} = 1/\text{Re}(Y_{22})$   $C_{\rm DS} + C_{\rm GD} = \text{Im}(Y_{22})/(2\pi f)$  $C_{\rm GS} + C_{\rm GD} = \text{Im}(Y_{11})/(2\pi f)$

$C_{\rm GS} + g_{\rm m} r_{\rm o} C_{\rm GD} = 1/{\rm Im}(Z_{11})/(2\pi f)$

$$R_{\rm NQS} = 1/(5g_{\rm m})$$

To fit the model to the measured data beyond the activity region of the transistor, series resistance and inductance associated with the gate, source and drain interconnects can be added and their values can be obtained by simulating gate, source and drain lines embedded in the oxide and substrate in an electromagnetic modeling and simulation software tool (such as Agilent Momentum). The component values calculated for the small signal model are listed in Table 1.

### The effect of NW density on extrinsic cutoff frequency

To explore the performance limit of InAs NW parallel array FETs, extrinsic cutoff frequency is calculated as a function of NW density using the formula described in the main text. The capacitance per NW is assumed to be independent of NW density. A previously reported saturation velocity for bulk InAs,  $v_{sat} \sim 1.3 \times 10^7$  cm/s at a field of 16 kV/cm (corresponding to  $V_{DS}$  = 2.5 V and  $L_G$  = 1.5 µm) was used for this analysis.<sup>2</sup>

**Figure S4**: The calculated cutoff frequency as a function of NW density for  $L_g=1.5 \mu m$ . Note that the parasitic capacitances are assumed to be the same as the experimental devices (Table 1). The dominant effect of increase the NW density is to reduce the  $C_{p,GS}/C_{ox}$  ratio per unit width, thereby increasing the cutoff frequency.

# References

- Baheri, M., Tsividis, Y. A small signal dc-to-high-frequency nonquasi-static model for four-terminal MOSFET valid in all regions of operation, *IEEE Trans. Electron Devices* 32, 2383–2391 (1985).

- Brennan, K., Hess, K. High field transport in GaAs, InP and InAs. Solid State Electron.

27, 347-357 (1984).